### The method

Derive stages from basic amplifier stage through application of error-reduction techniques

- Understand basic amplification with single transistor

- The biased CS stage

- Behavior of the intrinsic CS stage (ideal drive and load conditions) \* Static nonlinear behavior and design of voltage and current drive capability

- \* Dynamic nonlinear behavior

- \* Dynamic small-signal behavior

- \* Noise behavior

- Behavior of the CS stage when connected between a source and a load \* Small-signal dynamic behavior

- \* Noise behavior and optimization of the noise behavior

- Understand in which way the performance of a stage can be changed

- Change of operating point (design parameters: I and V)

- Change of geometry (design parameters: W and L) through application of error reduction techniques

- Application of balancing techniques: differential pair and push-pull stage

- Application of direct negative feedback: the CD and the CG stage

Application of indirect negative feedback: the current mirror and the voltage mirror

# CS basic amplifier stage

### The biased CS stage

- Output port biased for performance Input stage: noise

- Output stage: drive capability

Intermediate stages:

- \* Drive capability \* Contribution to

- LP product

- Differential error to gain ratio

(Vo) [uA]

015 02

$\bigcap_{10u}^{1ds0}$  Vo

- Vo [V]

0.05 0.10

Vi [V]

L = 180r

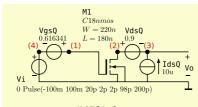

Vo(Vi) characterist

Vi [V]

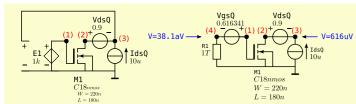

#### Behavior of the intrinsic CS stage Static nonlinear behavior

- All curves pass through the origin - Current sink capability exceeds current source capability (latter one limited by bias current)

lo(Vi) cha

-25 -0.20 -0.15 -0.10 -0.05 0.00

- Modeling of nonlinear effects is shown Other static transfers are not shown: \* Input resistance is infinite \* DC current gain is infinite \* DC current to voltage transfer is infinite

- Vo [V]

10

-0.5

-1.0 L

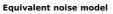

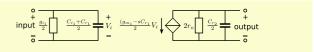

$=4kTR_s$

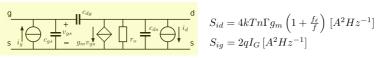

$S_{i_n} = 4kTn\Gamma g_m \left(1 + \frac{f_\ell}{f}\right)$

$S_{v_{R_s}}$

B =1  $D = -\frac{sc_{iss}}{a_{m}} = -\frac{s}{2\pi f_T}$

$S_{i_{n_G}} = 2qI_G$

Vo(lo) characteristic

Bias sources at input port depend on

- Biasing of particular device at simulation

temperature correct for all resistive port

device characteristics

terminations

Can be determined by SPICE

#### Noise behavior

Transformation into equivalent input sources:

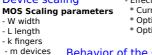

**Device scaling**

gate-induced noise.

$B = -\frac{1}{g_m}$

$D = -\frac{s}{s}$

- The noise source id D is called

- Different source and sink drive

for rising and falling edges

capability results in different slew rate

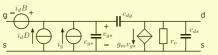

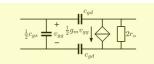

Right half-plane zero depend on trans-

conductance and thus on the current

Transmission-1 matrix parameters can

- All transfers have zero at:  $s = \frac{g_m}{c}$

Usually above the cut off frequency

Cut-off frequency:  $\omega_T = \frac{g_m}{c_{qs}+c_{qd}}$

÷

Dynamic small-signal behavior

be calculated from small-signal

equivalent circuit

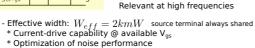

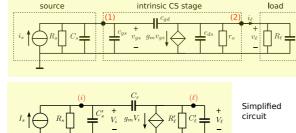

\* Optimization of device matching Behavior of the CS stage between source and load Small-signal dynamic behavior when driven/terminated from/with parallel RC

Qualitative description of the dynamic behavior (transimpedance gain) 1. If Cr=0, the circuit has two poles; associated with the two RC networks. 2. If C<sub>r</sub> is small with respect to the other capacitances, C<sub>r</sub> will not affect the product of the poles

The sum of the poles will be increased (Miller effect): one pole is closer to the origin, thus the other moves towards a higher frequency. This is called pole-splitting (due to capacitive feedback)

- A positive zero is found at:  $s = \frac{g_m}{a}$

Pole-splitting can be used for frequency compensation. Undesired pole-splitting may be a cause for bandwidth reduction in a feedback amplifier. This is the case if the high frequency pole is split out of the dominant group.

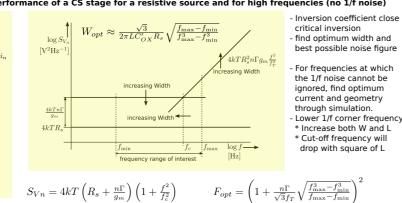

#### Optimization of the noise performance of a CS stage for a resistive source and for high frequencies (no 1/f noise)

Stages for CMOS Controller Design

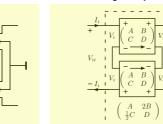

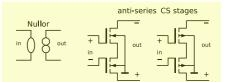

### Anti-series connected stages: differential pair

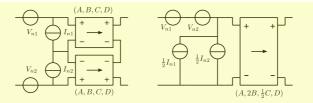

#### Concept 3- or 4-terminal networks Small-signal equivalent

#### - Behavior approximates that of natural two-port Biasing Common-mode current sources only

Topology

- 4-termina

Behavioral modifications

Large signal static behavior - Even terms cancel - Limiting current characteristic

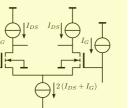

Small-signal dynamic Transmission coefficients A and D equal those of constituting elements Coefficient B twice as large Coefficient C half

#### Noise Behavior

Voltage noise spectrum twice as large - Current noise spectrum half that of constituting elements

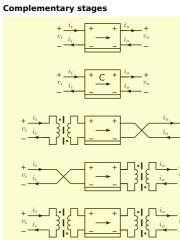

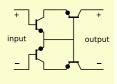

#### Complementary parallel stage: push-pull stage Topology

- Can be used as 4-terminal with split-signal output, but not a natural two-port

/diff\_in [V

#### Biasing

- Common-mode voltage sources only

- Large signal static behavior - Even terms cancel

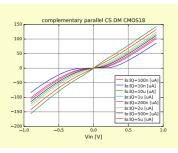

- Exapanding current characteristic Imperfect balancing PMOS and NMOS

- Small-signal dynamic - Transmission coefficients A and D equal

- those of consituting element - Coefficient B half

- Coefficient C twice as large

**Noise Behavior** Voltage noise spectrum half that of constituting elements

Current noise spectrum twice as large

source

## Local feedback stages

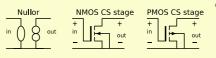

Basic nullor implementations

#### The CD stage or source follower Non-energic feedback unity-gain

#### voltage amplifier

- Behavioral modifications through application of negative feedback: \* Nonenergic: equivalent input noise sources equal

- those of its CS stage controller

- \* Parallel voltage sensing: decreases output impedance

- \* Series voltage comparison:

- increases input impedance

- Feedback not effective if sensing or comparison not possible: \* Output shorted

- \* Input current-driven

- Back-gate effect reduces loop gain

- Poles may be complex with capacitive load

#### The CG stage

#### Non-energic feedback unity-gain current amplifier

- Behavioral modifications through

- application of negative feedback: \* Nonenergic: equivalent input noise

- sources equal those of CS stage

- \* Series current sensing:

- increases output impedance \* Parallel current comparison:

- decreases input impedance

- Feedback not effective if sensing or

- comparison not possible

- \* Output left open

- \* Input voltage-driven

- Back-gate effect increases loop gain

- In practice a large loop gain if driven from and terminated with a CS stage

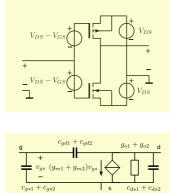

### Cascode stages

input

- CS-CG or CE-CB cascade = cascode stage - Elimination of pole-splitting (shorted CS or CE stage)

- Approximate unilateral behavior

- High output impedance - Non dominant pole of CG or CB stage at  $f_T$

- Almost ideal CS or CE stage

output

#### Balanced cascode stage

- Best possible single-stage nullor implementation

- Best possible single-stage natural two-port approximation

- Approximate unilateral behavior High output impedance

- Non dominant pole of balanced CG or CB stage at  $f_{\scriptscriptstyle T}$

#### Assume biased stages

Complementary parallel CS stage

| +<br>in | UĘ, | J⊱ | +<br>out |

|---------|-----|----|----------|

|         |     |    |          |

### Local feedback stages

- Feedback with a basic amplifier stage as controller 3 terminal controller:

- \* CS stage

- \* Complementary-parallel stage 4-terminal controller

- \* Anti-series stage