#### **Structured Electronic Design**

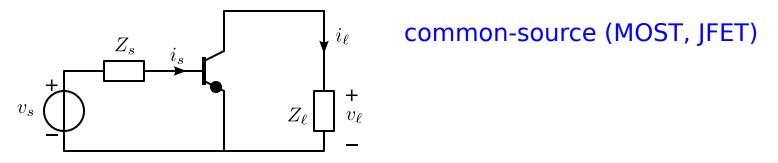

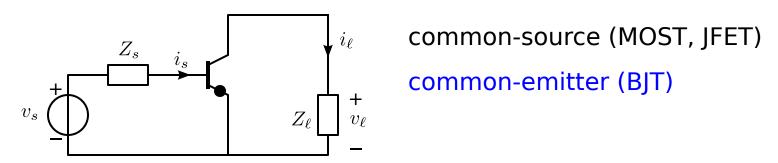

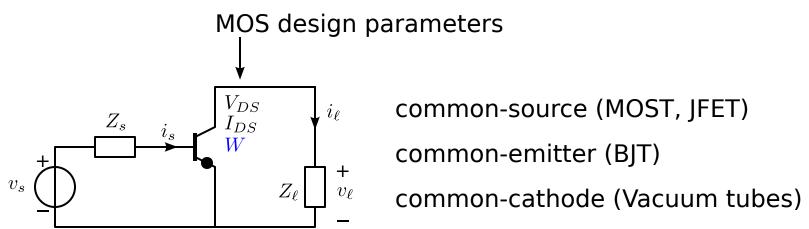

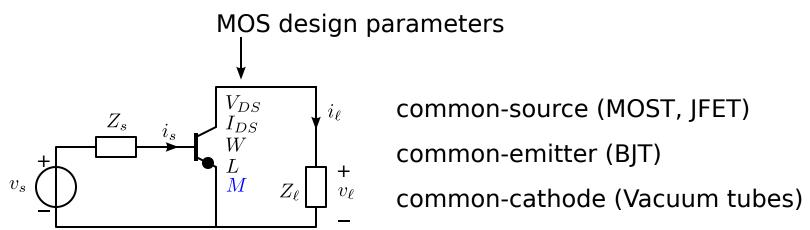

CS stage Introduction

Anton J.M. Montagne

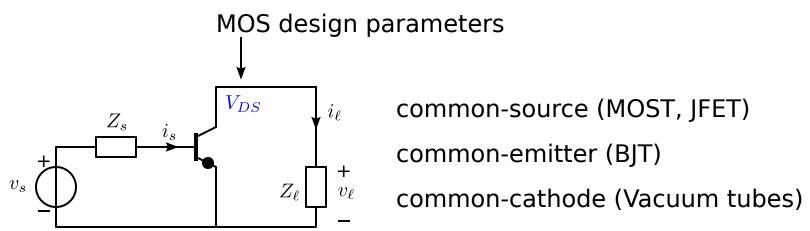

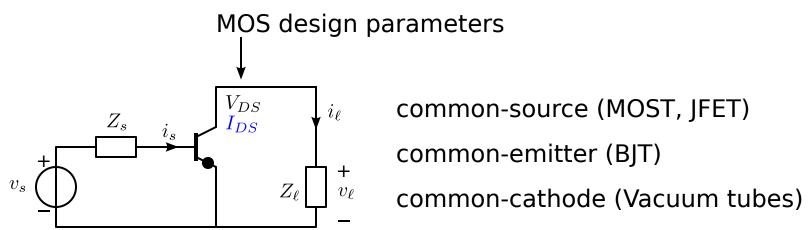

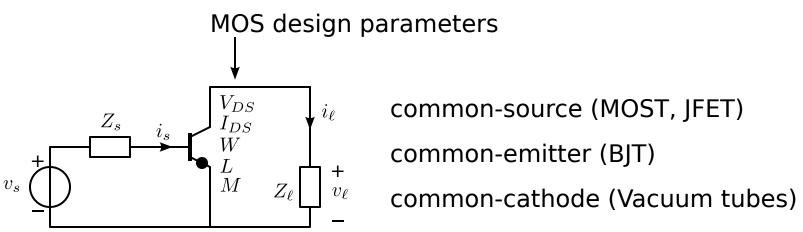

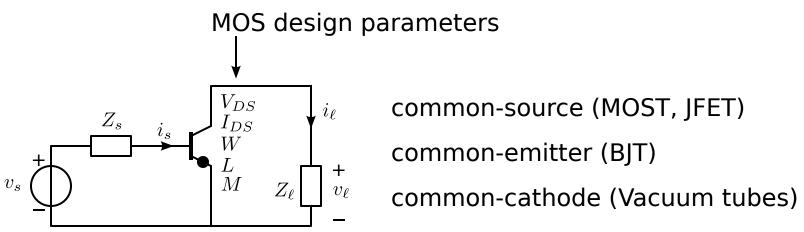

### CS stage static and dynamic behavior

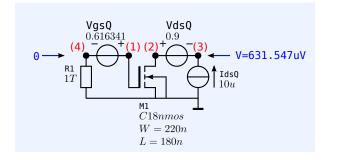

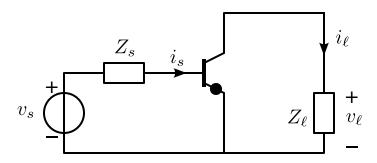

biased stage

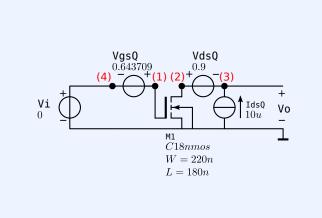

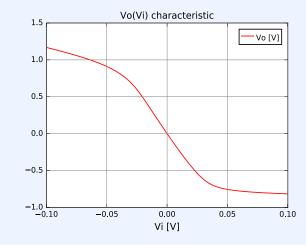

static voltage drive capability

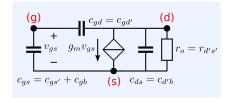

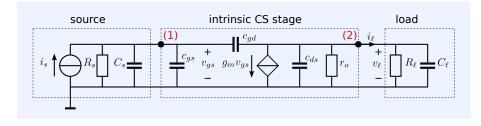

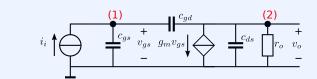

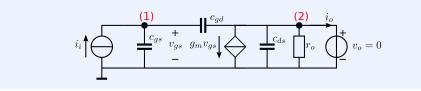

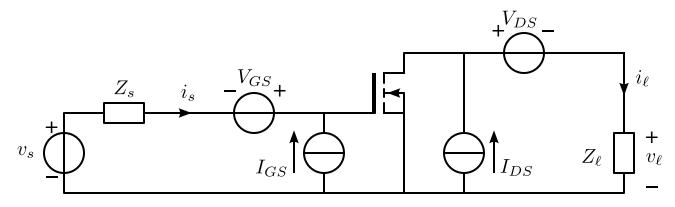

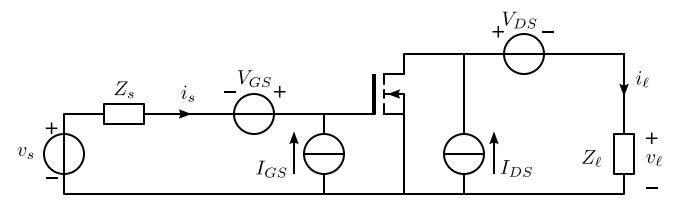

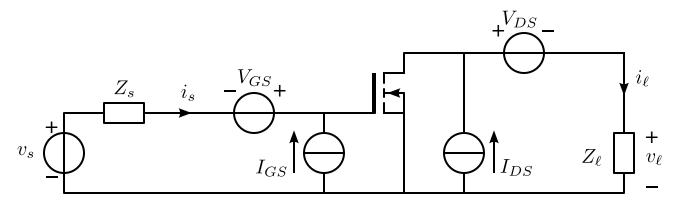

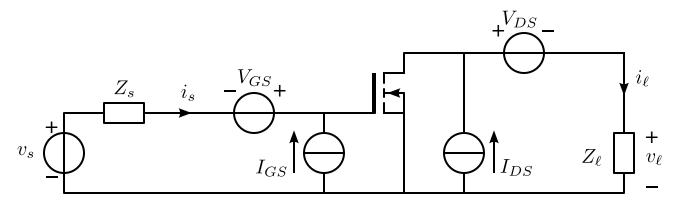

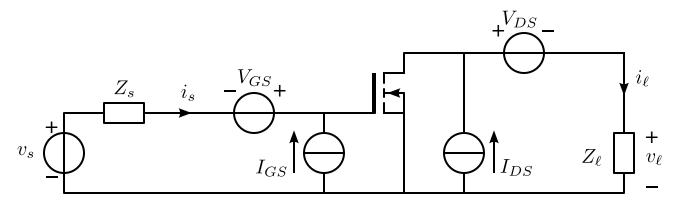

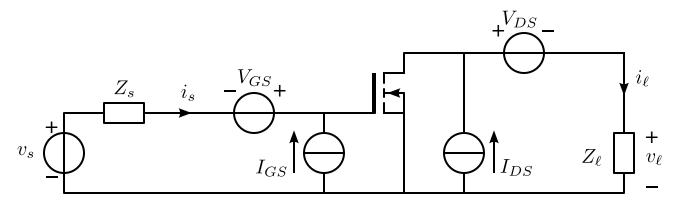

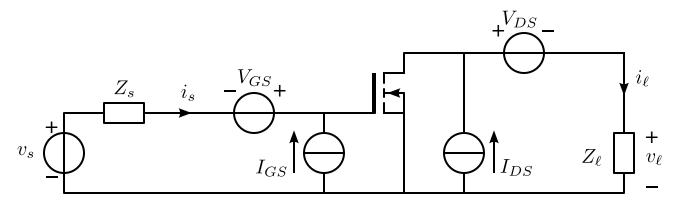

small-signal model

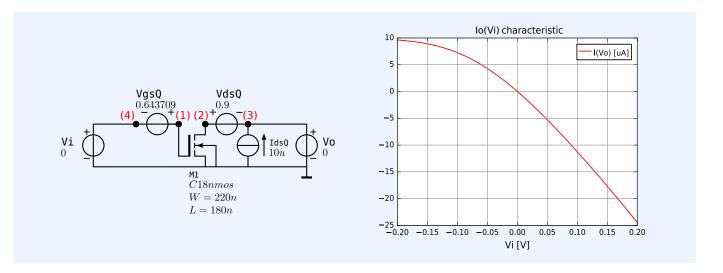

static current drive capability

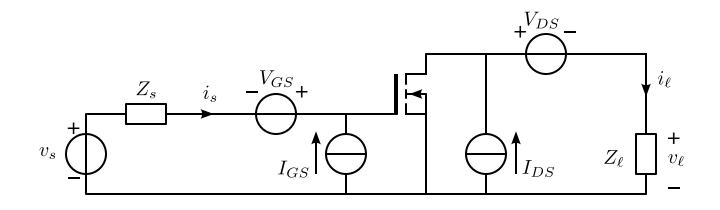

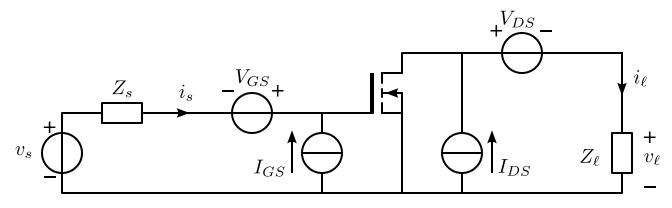

small-signal source-to-load transfer

small-signal transimpedance

Study behavior

Find design parameters for performance aspects

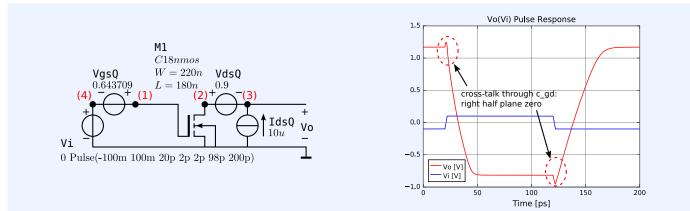

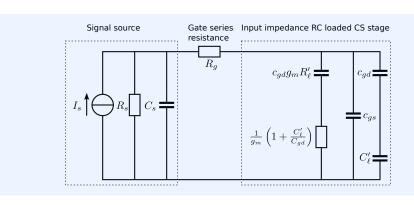

dynamic voltage drive capability

#### small-signal current gain

#### small-signal voltage driven

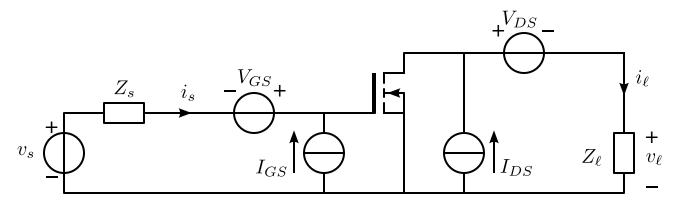

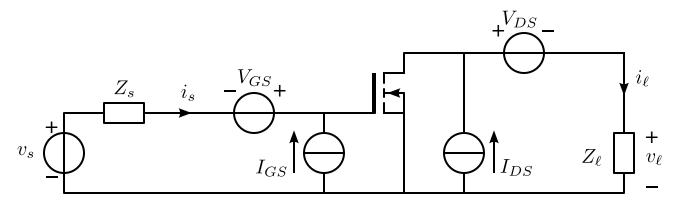

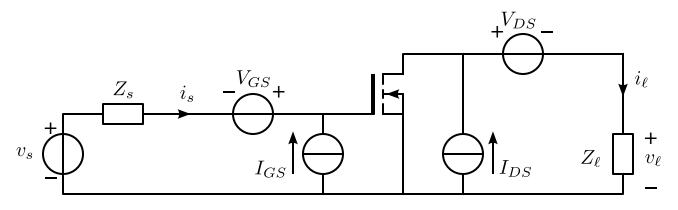

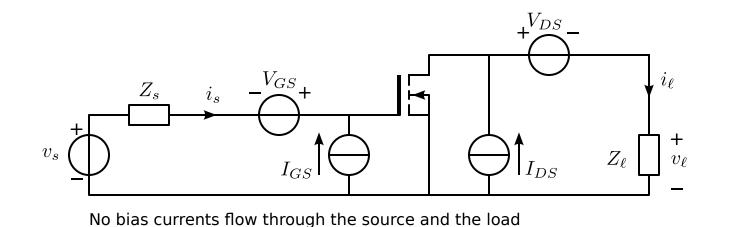

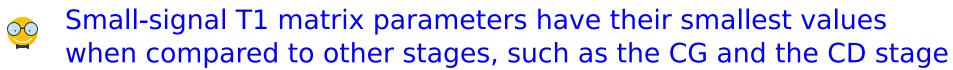

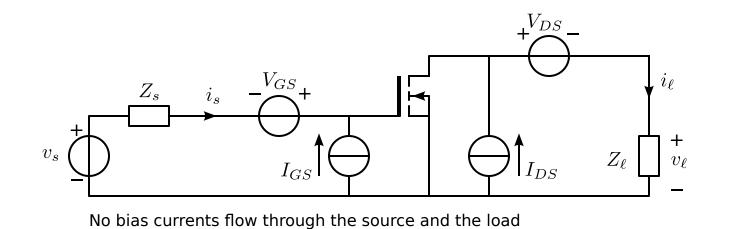

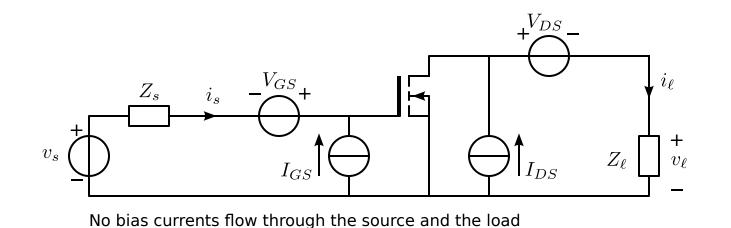

No bias currents flow through the source and the load

No bias currents flow through the source and the load

No bias currents flow through the source and the load  $(v_s, v_\ell), (v_s, i_\ell), (i_s, v_\ell), (i_s, i_\ell)$  characteristics pass through the origin

Biased CS (MOST, No bias currents fl $(v_s, v_\ell), (v_s, i_\ell), (v_s, i_\ell)$

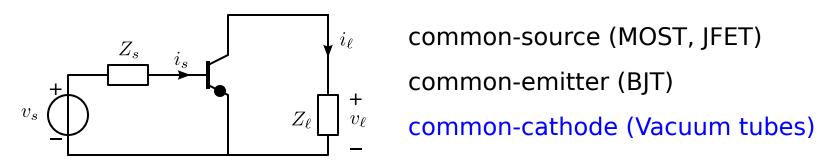

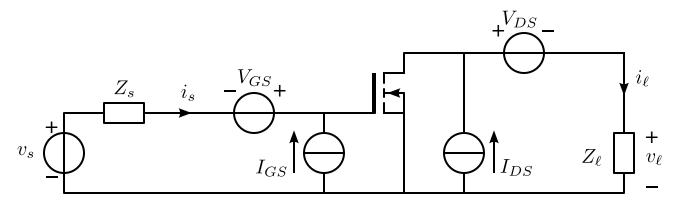

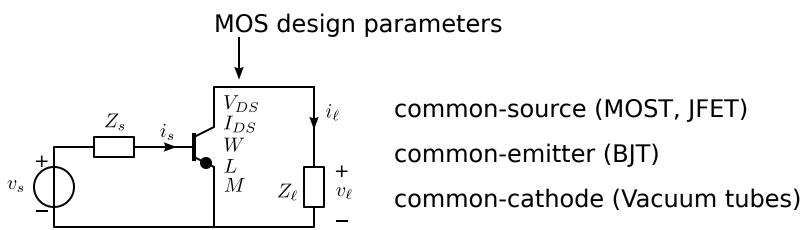

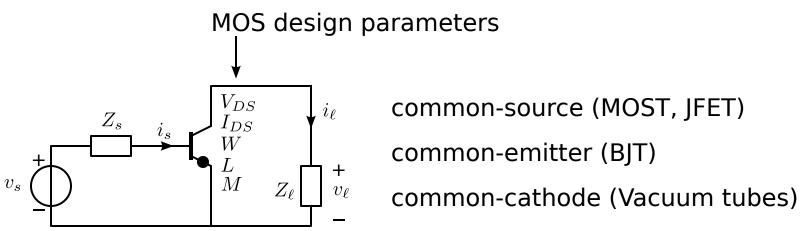

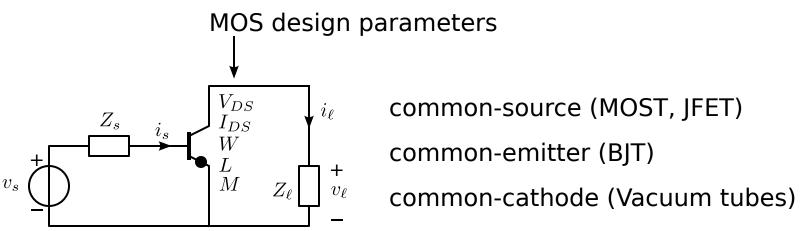

Biased CS (MOST, JFET), CE (BJT) or CC (triode, pentode) stage

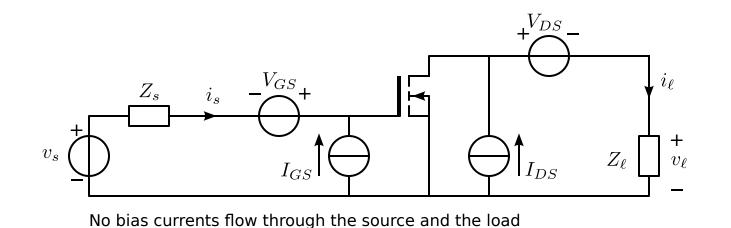

No bias currents flow through the source and the load

No bias currents flow through the source and the load  $(v_s,v_\ell),\,(v_s,i_\ell),\,(i_s,v_\ell),\,(i_s,i_\ell)$  characteristics pass through the origin

Biased CS (MOST, JFET), CE (BJT) or CC (triode, pentode) stage No bias currents flow through the source and the load

No bias currents flow through the source and the load  $(v_s,v_\ell),\,(v_s,i_\ell),\,(i_s,v_\ell),\,(i_s,i_\ell)$  characteristics pass through the origin

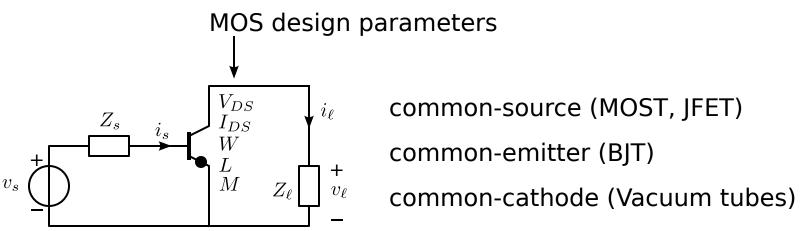

Biased CS (MOST, JFET), CE (BJT) or CC (triode, pentode) stage No bias currents flow through the source and the load

- Biased CS (MOST, JFET), CE (BJT) or CC (triode, pentode) stage No bias currents flow through the source and the load

- $(v_s,v_\ell),\,(v_s,i_\ell),\,(i_s,v_\ell),\,(i_s,i_\ell)$  characteristics pass through the origin

Biased CS (MOST, No bias currents fl $(v_s, v_\ell), (v_s, i_\ell), (v_s, i_\ell)$

- Biased CS (MOST, JFET), CE (BJT) or CC (triode, pentode) stage

- No bias currents flow through the source and the load

- $(v_s,v_\ell),\,(v_s,i_\ell),\,(i_s,v_\ell),\,(i_s,i_\ell)$  characteristics pass through the origin

Biased CS (MOST, No bias currents fl $(v_s, v_\ell), (v_s, i_\ell), (v_s, i_\ell)$

- Biased CS (MOST, JFET), CE (BJT) or CC (triode, pentode) stage

- No bias currents flow through the source and the load

- $(v_s,v_\ell),\,(v_s,i_\ell),\,(i_s,v_\ell),\,(i_s,i_\ell)$  characteristics pass through the origin

Biased CS (MOST, No bias currents fl $(v_s, v_\ell), (v_s, i_\ell), (v_s, i_\ell)$

- Biased CS (MOST, JFET), CE (BJT) or CC (triode, pentode) stage

- No bias currents flow through the source and the load

- $(v_s,v_\ell),\,(v_s,i_\ell),\,(i_s,v_\ell),\,(i_s,i_\ell)$  characteristics pass through the origin

Biased CS (MOST, No bias currents fl $(v_s, v_\ell), (v_s, i_\ell), (v_s, i_\ell)$

- Biased CS (MOST, JFET), CE (BJT) or CC (triode, pentode) stage

- No bias currents flow through the source and the load

- $(v_s,v_\ell),\,(v_s,i_\ell),\,(i_s,v_\ell),\,(i_s,i_\ell)$  characteristics pass through the origin

Biased CS (MOST, No bias currents fl $(v_s, v_\ell), (v_s, i_\ell), (v_s, i_\ell)$

- Biased CS (MOST, JFET), CE (BJT) or CC (triode, pentode) stage

- No bias currents flow through the source and the load

- $(v_s,v_\ell),\,(v_s,i_\ell),\,(i_s,v_\ell),\,(i_s,i_\ell)$  characteristics pass through the origin

Biased CS (MOST, No bias currents fl $(v_s, v_\ell), (v_s, i_\ell), (v_s, i_\ell)$

- Biased CS (MOST, JFET), CE (BJT) or CC (triode, pentode) stage

- No bias currents flow through the source and the load

- $(v_s,v_\ell),\,(v_s,i_\ell),\,(i_s,v_\ell),\,(i_s,i_\ell)$  characteristics pass through the origin

No bias currents flow through the source and the load  $(v_s, v_\ell), (v_s, i_\ell), (i_s, v_\ell), (i_s, i_\ell)$  characteristics pass through the origin

#### Why is the CS stage the basic MOS amplifier stage?

- Biased CS (MOST, JFET), CE (BJT) or CC (triode, pentode) stage

- No bias currents flow through the source and the load

- $(v_s,v_\ell),\,(v_s,i_\ell),\,(i_s,v_\ell),\,(i_s,i_\ell)$  characteristics pass through the origin

$(v_s,v_\ell),\,(v_s,i_\ell),\,(i_s,v_\ell),\,(i_s,i_\ell)$  characteristics pass through the origin

Why is the CS stage the *basic* MOS amplifier stage? ÓÒ

Biased CS (MOST, JFET), CE (BJT) or CC (triode, pentode) stage No bias currents flow through the source and the load

$(v_s,v_\ell),\,(v_s,i_\ell),\,(i_s,v_\ell),\,(i_s,i_\ell)$  characteristics pass through the origin

Why is the CS stage the *basic* MOS amplifier stage? 60

Small-signal T1 matrix parameters have their smallest values when compared to other stages, such as the CG and the CD stage

This makes it the best possible single-stage approximation of a nullor: the ideal controller for negative feedback amplifiers

$(v_s,v_\ell),\,(v_s,i_\ell),\,(i_s,v_\ell),\,(i_s,i_\ell)$  characteristics pass through the origin

Why is the CS stage the *basic* MOS amplifier stage? 60

Small-signal T1 matrix parameters have their smallest values when compared to other stages, such as the CG and the CD stage

This makes it the best possible single-stage approximation of a nullor: the ideal controller for negative feedback amplifiers

As a matter of fact, we will see that the CG and the CC stage can be considered as feedback stages that have a CS stage as controller

$(v_s, v_\ell), (v_s, i_\ell), (i_s, v_\ell), (i_s, i_\ell)$  characteristics pass through the origin

#### Why is the CS stage the *basic* MOS amplifier stage? 60

Small-signal T1 matrix parameters have their smallest values when compared to other stages, such as the CG and the CD stage

This makes it the best possible single-stage approximation of a nullor: the ideal controller for negative feedback amplifiers

As a matter of fact, we will see that the CG and the CC stage can be considered as feedback stages that have a CS stage as controller

The performance of feedback stages will be related to that of the CS stage considering the error reduction capabilities of negative feedback

$(v_s, v_\ell), (v_s, i_\ell), (i_s, v_\ell), (i_s, i_\ell)$  characteristics pass through the origin

#### Why is the CS stage the *basic* MOS amplifier stage? 60

Small-signal T1 matrix parameters have their smallest values when compared to other stages, such as the CG and the CD stage

This makes it the best possible single-stage approximation of a nullor: the ideal controller for negative feedback amplifiers

As a matter of fact, we will see that the CG and the CC stage can be considered as feedback stages that have a CS stage as controller

The performance of feedback stages will be related to that of the CS stage considering the error reduction capabilities of negative feedback

So we only need to study the CS stage in detail?

So we only need to study the CS stage in detail?

Yes, the behavior of other stages will be derived from that of the CS stage.

- So we only need to study the CS stage in detail? 60

- Yes, the behavior of other stages will be derived from that of the CS stage.

- What do we need to know about the CS stage? 60

- So we only need to study the CS stage in detail? 60

- Yes, the behavior of other stages will be derived from that of the CS stage.

- What do we need to know about the CS stage? 60

- We need to know in which way and to what extend  $\bigcirc$ its performance can be affected by design.

- So we only need to study the CS stage in detail? 60

- Yes, the behavior of other stages will be derived from that of the CS stage.

- What do we need to know about the CS stage? 60

- We need to know in which way and to what extend  $\bigcirc$ its performance can be affected by design.

#### Performance? ÓÒ

- So we only need to study the CS stage in detail? ÓÓ

- Yes, the behavior of other stages will be derived from that of the CS stage.

- What do we need to know about the CS stage? 60

- We need to know in which way and to what extend  $\bigcirc \bigcirc$ its performance can be affected by design.

- Performance? 60

- Voltage and current drive capability

- So we only need to study the CS stage in detail? 60

- Yes, the behavior of other stages will be derived from that of the CS stage.

- What do we need to know about the CS stage? 60

- We need to know in which way and to what extend 0-0 its performance can be affected by design.

- Performance? 60

- Voltage and current drive capability

- $\bigodot$ Noise performance

- So we only need to study the CS stage in detail? 60

- Yes, the behavior of other stages will be derived from that of the CS stage.

- What do we need to know about the CS stage? ÓÒ

- We need to know in which way and to what extend 0-0 its performance can be affected by design.

- Performance? 60

- Voltage and current drive capability  $\bigcirc$

- Noise performance  $\bigcirc$

- Temperature dependency  $\bigcirc$

- So we only need to study the CS stage in detail? 60

- Yes, the behavior of other stages will be derived from that of the CS stage.

- What do we need to know about the CS stage? 60

- We need to know in which way and to what extend <del>...</del> its performance can be affected by design.

- Performance? 60

- Voltage and current drive capability  $\bigcirc$

- Noise performance  $\bigcirc$

- Temperature dependency  $\bigcirc$

- Bandwidth and frequency response

- So we only need to study the CS stage in detail? 60

- Yes, the behavior of other stages will be derived from that of the CS stage.

- What do we need to know about the CS stage? 60

- We need to know in which way and to what extend <del>...</del> its performance can be affected by design.

- Performance? 60

- Voltage and current drive capability  $\bigcirc$

- Noise performance

- Temperature dependency  $\bigcirc$

- Bandwidth and frequency response  $\bigcirc \bigcirc$

Design?

- So we only need to study the CS stage in detail? 60

- Yes, the behavior of other stages will be derived from that of the CS stage.

- What do we need to know about the CS stage? 60

- We need to know in which way and to what extend <del>...</del> its performance can be affected by design.

- Performance? 60

- Voltage and current drive capability

- Noise performance

- Temperature dependency  $\bigcirc$

- Bandwidth and frequency response  $\bigcirc \bigcirc$

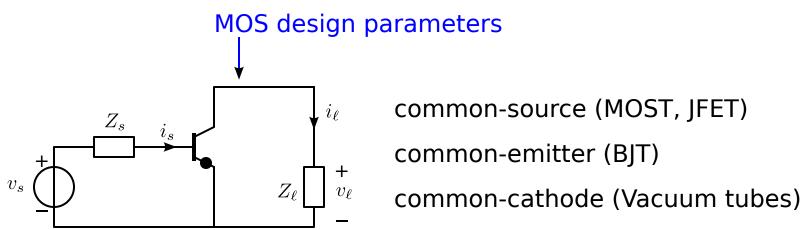

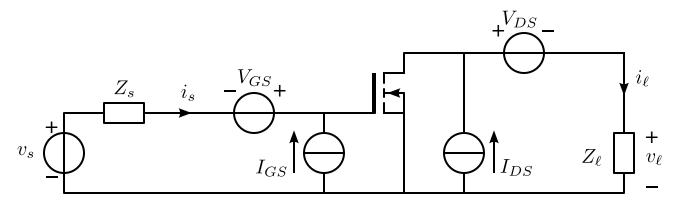

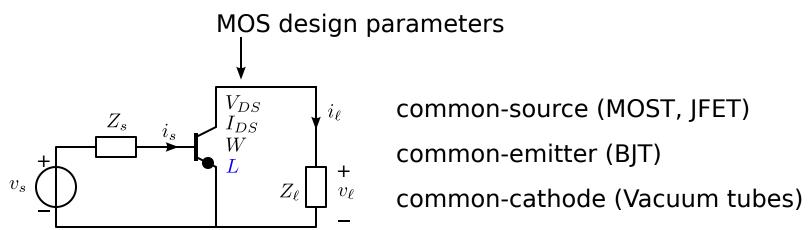

#### Design? Channel width

<u>´0 Ò`</u>

- So we only need to study the CS stage in detail? 60

- Yes, the behavior of other stages will be derived from that of the CS stage.

- What do we need to know about the CS stage? ÓÒ

- We need to know in which way and to what extend <del>...</del> its performance can be affected by design.

- Performance? 60

- Voltage and current drive capability

- Noise performance 00

- Temperature dependency  $\bigcirc$

- Bandwidth and frequency response  $\bigcirc \bigcirc$

#### Design?

<u>´0 Ò`</u>

🥸 Channel width

Channel length Q

- So we only need to study the CS stage in detail? 60

- Yes, the behavior of other stages will be derived from that of the CS stage.

- What do we need to know about the CS stage? ÓÒ

- We need to know in which way and to what extend 0-0 its performance can be affected by design.

- Performance? 60

- Voltage and current drive capability

- Noise performance 00

- Temperature dependency  $\bigcirc$

- Bandwidth and frequency response  $\bigcirc \bigcirc \bigcirc$

#### Design?

<u>´0 Ò`</u>

- 🥸 Channel width

- Q Channel length

- Number of sections **O**

- So we only need to study the CS stage in detail? 60

- Yes, the behavior of other stages will be derived from that of the CS stage.

- What do we need to know about the CS stage? 60

- We need to know in which way and to what extend 0-0 its performance can be affected by design.

- Performance? 60

- Voltage and current drive capability

- Noise performance 00

- Temperature dependency  $\bigcirc$

- Bandwidth and frequency response  $\bigcirc \bigcirc \bigcirc$

#### Design?

- 🤨 Channel width

- O Channel length

- Number of sections **O**

- Operating current and voltage

- So we only need to study the CS stage in detail? 60

- Yes, the behavior of other stages will be derived from that of the CS stage.

- What do we need to know about the CS stage? 60

- We need to know in which way and to what extend 0-0 its performance can be affected by design.

- Performance? <mark>6 0</mark>

- Voltage and current drive capability

- Noise performance 00

- Temperature dependency  $\bigcirc$

- Bandwidth and frequency response  $\bigcirc \bigcirc$

Can these performance aspects be designed independently?

#### Design?

- 🥸 Channel width

- O Channel length

- Number of sections

- Operating current and voltage **O**

- So we only need to study the CS stage in detail?

- Yes, the behavior of other stages will be derived from that of the CS stage.

- What do we need to know about the CS stage? 60

- We need to know in which way and to what extend 0-0 its performance can be affected by design.

- Performance?

- Voltage and current drive capability

- Noise performance

- Temperature dependency  $\bigcirc$

- Bandwidth and frequency response  $\bigcirc \bigcirc$

- Can these performance aspects be designed independently?

- Not in a single CS stage, but later we will present a design method that facilitates orthogonal design of the performance aspects of amplifiers.

#### Design?

- 🥸 Channel width

- Channel length

- Number of sections

- Operating current and voltage

- So we only need to study the CS stage in detail?

- Yes, the behavior of other stages will be derived from that of the CS stage.

- What do we need to know about the CS stage? 60

- We need to know in which way and to what extend 0-0 its performance can be affected by design.

- Performance?

- Voltage and current drive capability

- Noise performance

- Temperature dependency  $\bigcirc$

- Bandwidth and frequency response  $\bigcirc \bigcirc$

- Can these performance aspects be designed independently?

- Not in a single CS stage, but later we will present a design method that facilitates orthogonal design of the performance aspects of amplifiers. 📪

#### Design?

- 🥸 Channel width

- Channel length

- Number of sections

- Operating current and voltage