## **Structured Electronic Design**

MOS EKV model

Anton J.M. Montagne

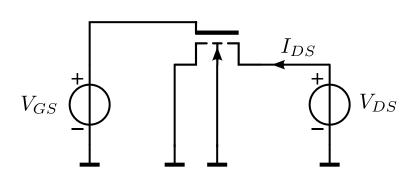

#### **PMOS**

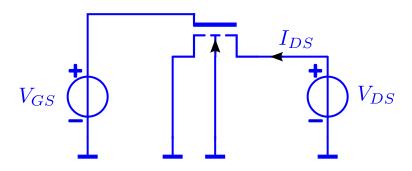

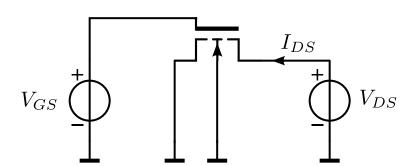

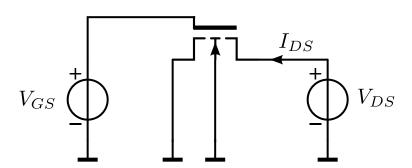

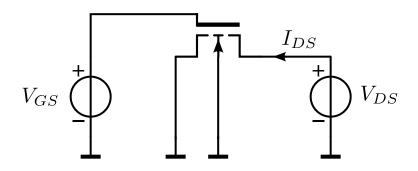

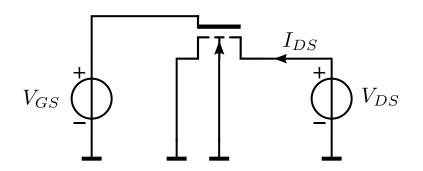

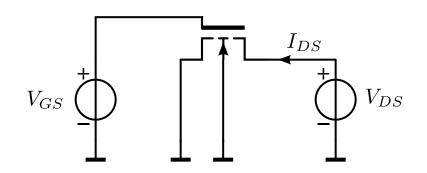

$$V_{GS}=0,\,V_{DS}>0\,$$

No current flow  $V_{GS}>0,\,V_{DS}>>0\,$

## MOS operation

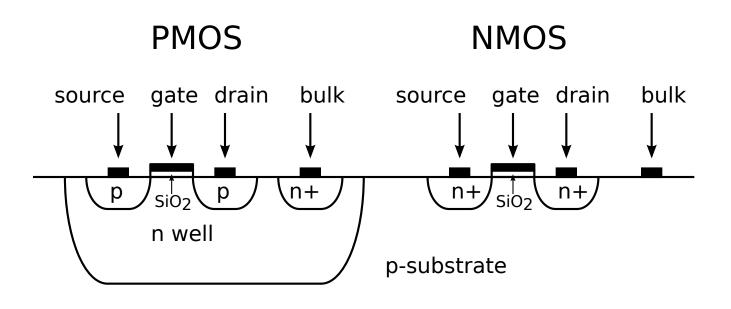

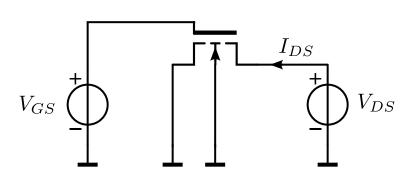

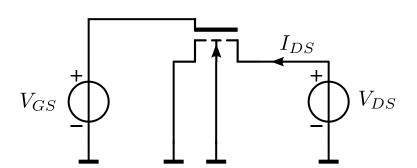

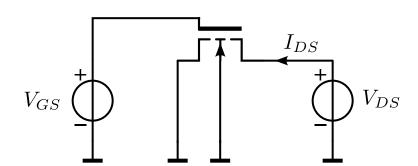

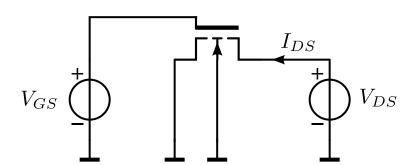

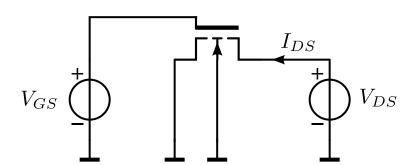

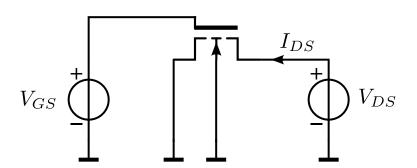

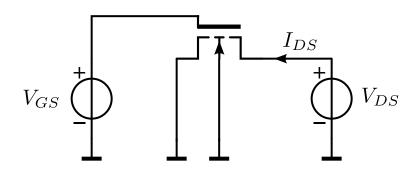

$$V_{GS}=0,\,V_{DS}>0\,$$

No current flow

$$V_{GS} > 0, V_{DS} >> 0$$

Surface potential at oxide-Si interface rises

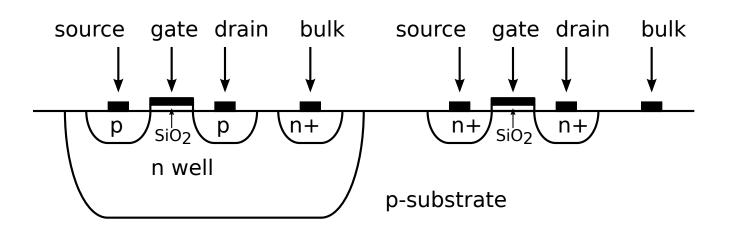

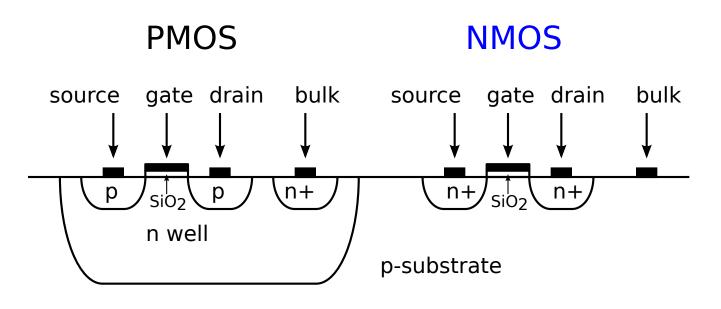

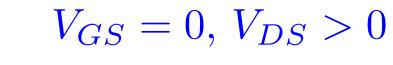

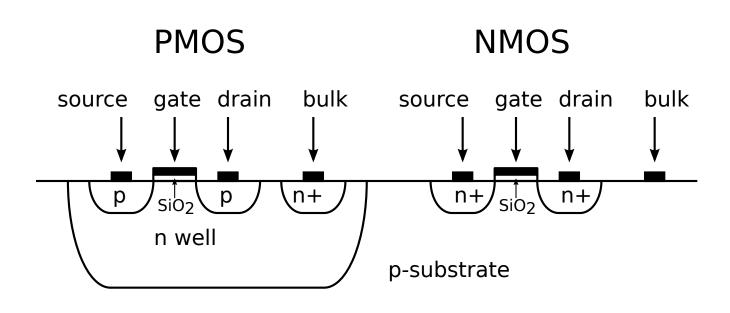

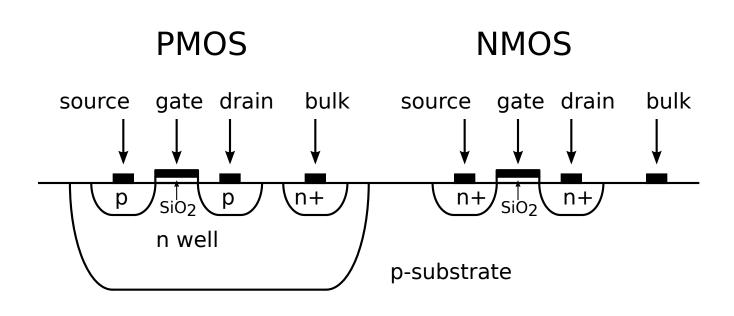

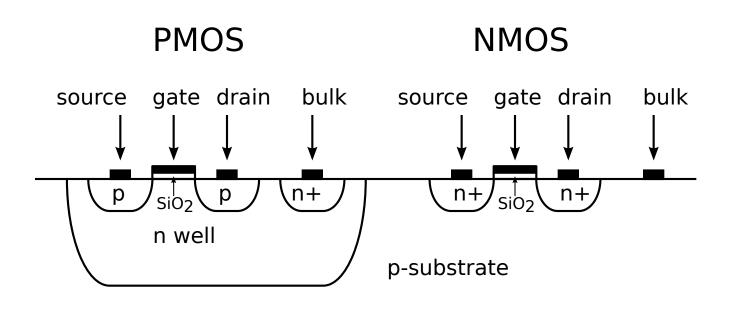

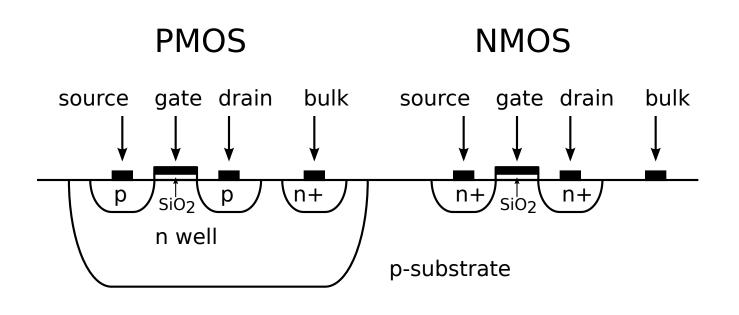

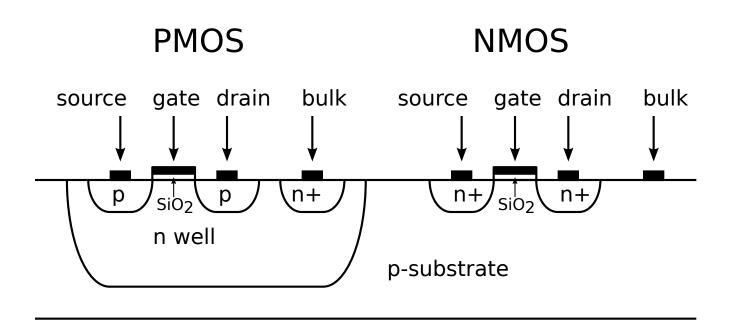

#### **PMOS NMOS** source gate drain gate drain bulk \n+ n+/ n well p-substrate

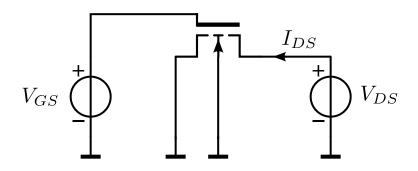

# MOS operation

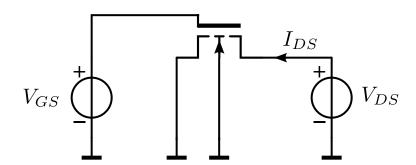

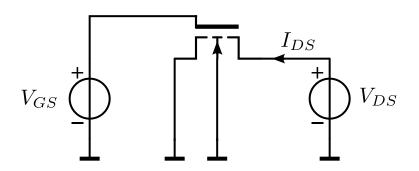

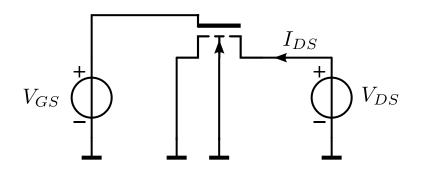

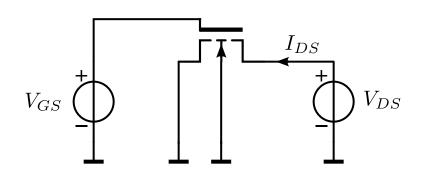

$$V_{GS}=0,\,V_{DS}>0\,$$

No current flow

$$V_{GS} > 0, V_{DS} >> 0$$

Surface potential at oxide-Si interface rises

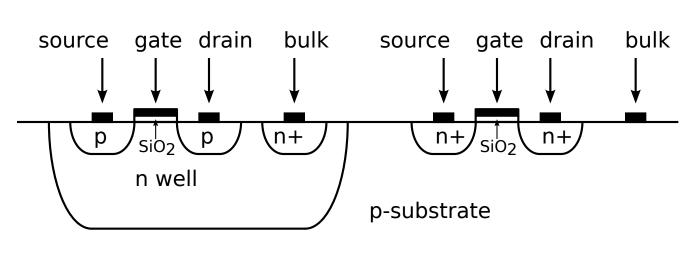

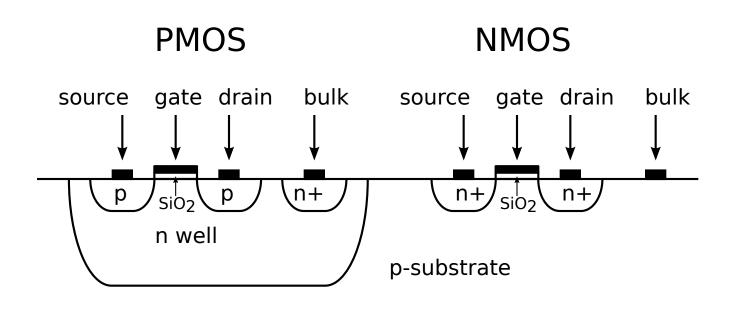

# PMOS source gate drain bulk source gate drain bulk p sio2 p n+ n+ sio2 n+ n well p-substrate

## MOS operation

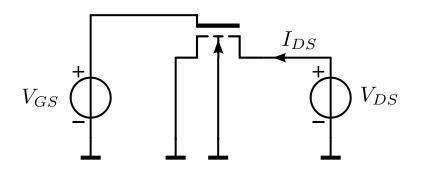

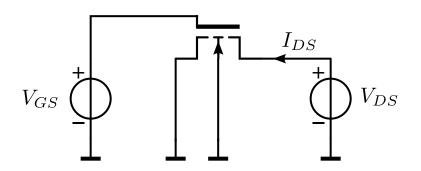

$$V_{GS}=0,\,V_{DS}>0\,$$

No current flow

$$V_{GS} > 0, V_{DS} >> 0$$

Surface potential at oxide-Si interface rises

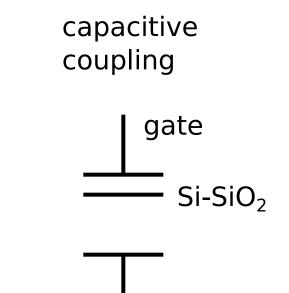

capacitive coupling

## MOS operation

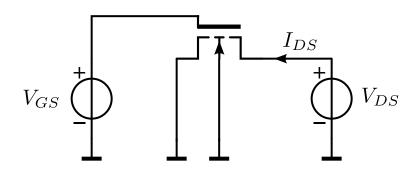

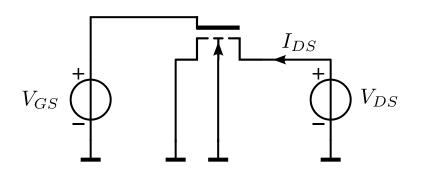

$$V_{GS}=0,\,V_{DS}>0\,$$

No current flow

$$V_{GS} > 0, V_{DS} >> 0$$

Surface potential at oxide-Si interface rises

capacitive coupling

## MOS operation

$$V_{GS}=0,\,V_{DS}>0\,$$

No current flow

$$V_{GS} > 0, V_{DS} >> 0$$

Surface potential at oxide-Si interface rises Source injects electrons in p region capacitive coupling

Tbulk

$$V_{GS}=0,\,V_{DS}>0\,$$

No current flow

$$V_{GS} > 0, V_{DS} >> 0$$

Surface potential at oxide-Si interface rises Source injects electrons in p region Weak inversion capacitive coupling

bulk

$$V_{GS}=0,\,V_{DS}>0\,$$

No current flow

$$V_{GS} > 0, V_{DS} >> 0$$

Surface potential at oxide-Si interface rises Source injects electrons in p region Weak inversion

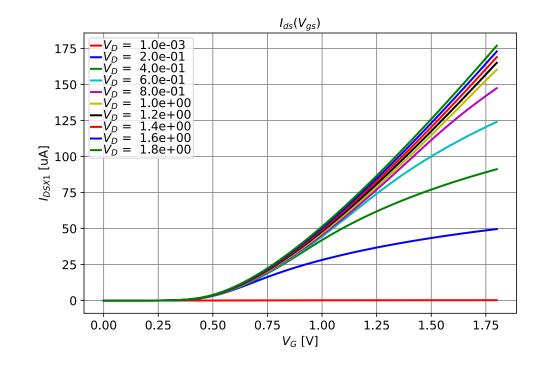

Drain current increases exponentially with the gate-source voltage

capacitive coupling

$$V_{GS}=0,\,V_{DS}>0\,$$

No current flow

$$V_{GS} > 0, V_{DS} >> 0$$

Surface potential at oxide-Si interface rises Source injects electrons in p region Weak inversion

Drain current increases exponentially with the gate-source voltage

$$V_{GS} > V_{th}, V_{DS} > V_{GS} - V_{th}$$

capacitive coupling

$$V_{GS}=0,\,V_{DS}>0\,$$

No current flow

$$V_{GS} > 0, V_{DS} >> 0$$

Surface potential at oxide-Si interface rises Source injects electrons in p region Weak inversion

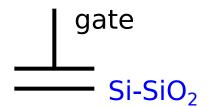

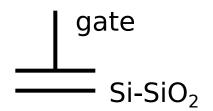

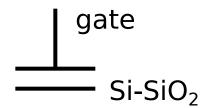

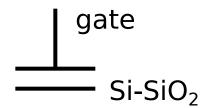

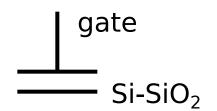

coupling gate Si-SiO<sub>2</sub>

capacitive

Drain current increases exponentially with the gate-source voltage

$$V_{GS} > V_{th}, V_{DS} > V_{GS} - V_{th}$$

An n-channel is established between source and drain

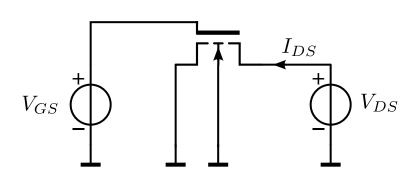

$$V_{GS}=0,\,V_{DS}>0\,$$

No current flow

$$V_{GS} > 0, V_{DS} >> 0$$

Surface potential at oxide-Si interface rises Source injects electrons in p region Weak inversion

capacitive coupling

gate

Si-SiO<sub>2</sub>

Drain current increases exponentially with the gate-source voltage

$$V_{GS} > V_{th}, V_{DS} > V_{GS} - V_{th}$$

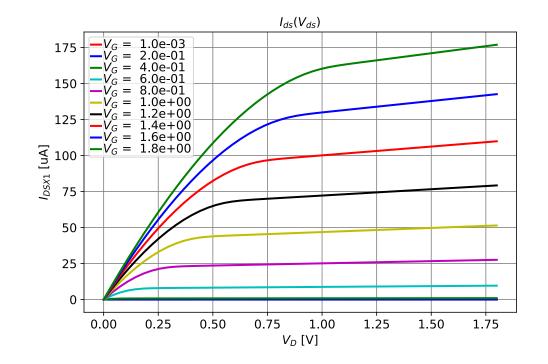

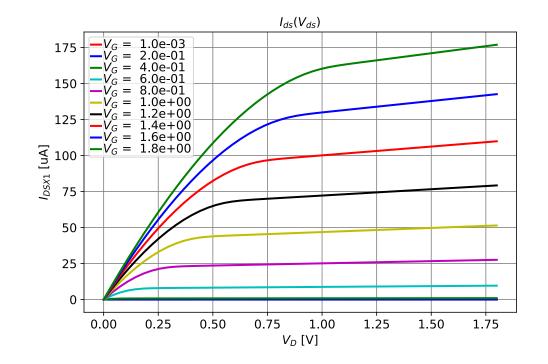

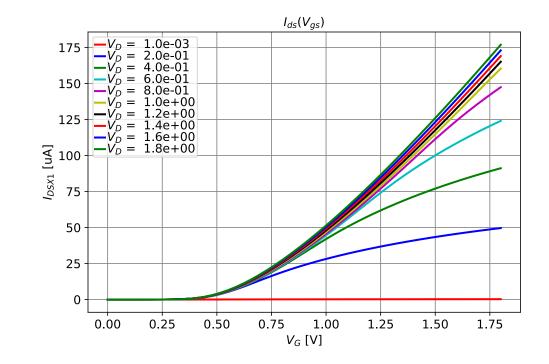

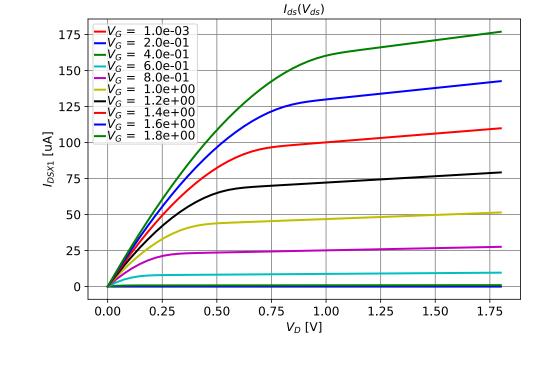

Drain-source voltage dependency

## MOS operation

$$V_{GS}=0,\,V_{DS}>0\,$$

No current flow

$$V_{GS} > 0, V_{DS} >> 0$$

Surface potential at oxide-Si interface rises Source injects electrons in p region Weak inversion capacitive coupling

gate

Si-SiO<sub>2</sub>

Drain current increases exponentially with the gate-source voltage

$$V_{GS} > V_{th}, V_{DS} > V_{GS} - V_{th}$$

#### Drain-source voltage dependency

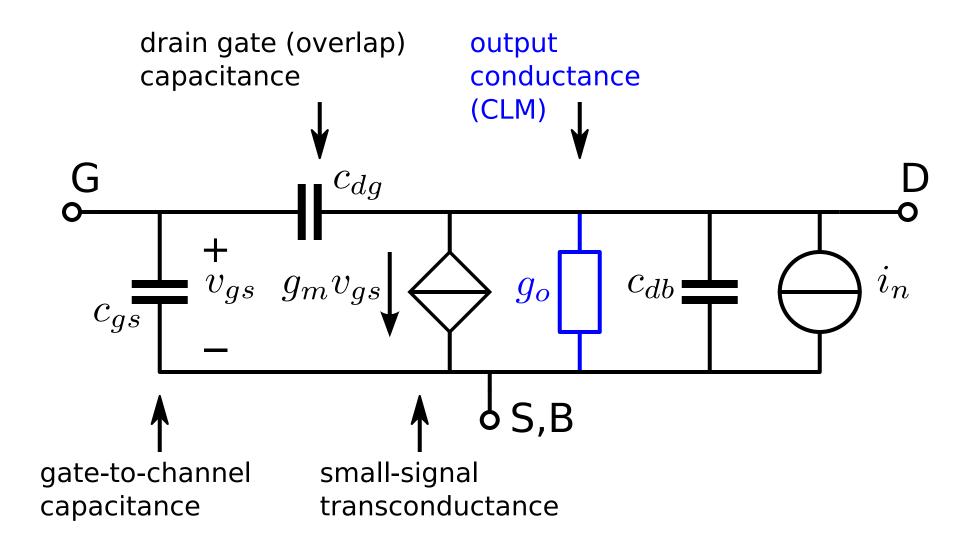

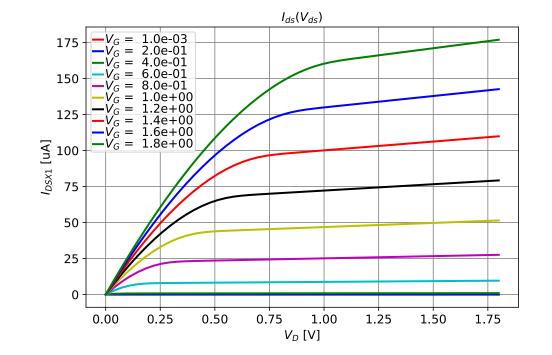

Channel length modulation (CLM)

## MOS operation

$$V_{GS}=0,\,V_{DS}>0\,$$

No current flow

$$V_{GS} > 0, V_{DS} >> 0$$

Surface potential at oxide-Si interface rises Source injects electrons in p region Weak inversion capacitive coupling

gate

Si-SiO<sub>2</sub>

Drain current increases exponentially with the gate-source voltage

$$V_{GS} > V_{th}, V_{DS} > V_{GS} - V_{th}$$

#### Drain-source voltage dependency

Channel length modulation (CLM)

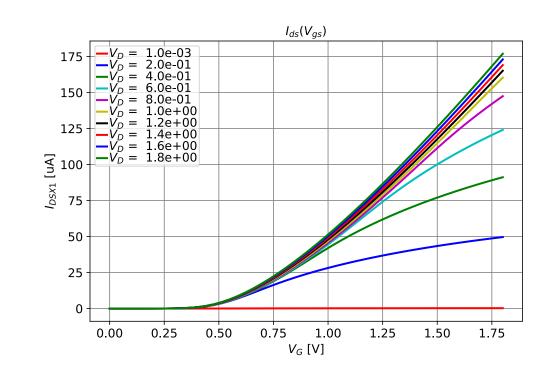

Drain current increases with drain-source voltage

## MOS operation

$$V_{GS}=0,\,V_{DS}>0\,$$

No current flow

$$V_{GS} > 0, V_{DS} >> 0$$

Surface potential at oxide-Si interface rises Source injects electrons in p region Weak inversion capacitive coupling

gate

Si-SiO<sub>2</sub>

Drain current increases exponentially with the gate-source voltage

$$V_{GS} > V_{th}, V_{DS} > V_{GS} - V_{th}$$

#### Drain-source voltage dependency

Channel length modulation (CLM)

Drain current increases with drain-source voltage Breakdown

# MOS operation

$$V_{GS}=0,\,V_{DS}>0\,$$

No current flow

$$V_{GS} > 0, V_{DS} >> 0$$

Surface potential at oxide-Si interface rises Source injects electrons in p region Weak inversion capacitive coupling

gate

Si-SiO<sub>2</sub>

Drain current increases exponentially with the gate-source voltage

$$V_{GS} > V_{th}, V_{DS} > V_{GS} - V_{th}$$

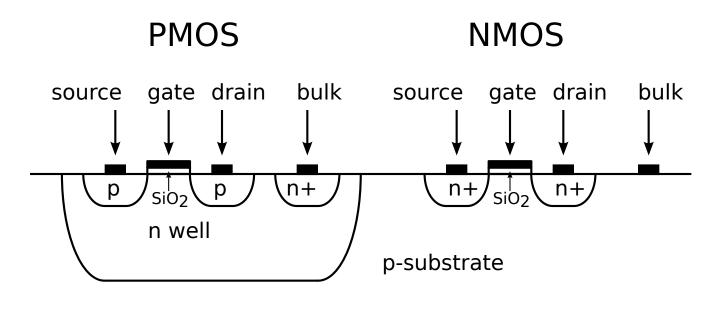

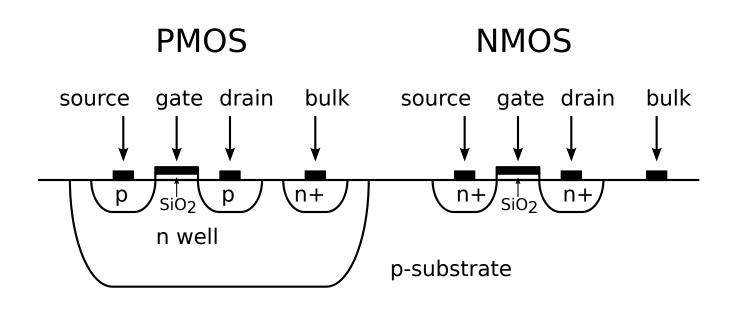

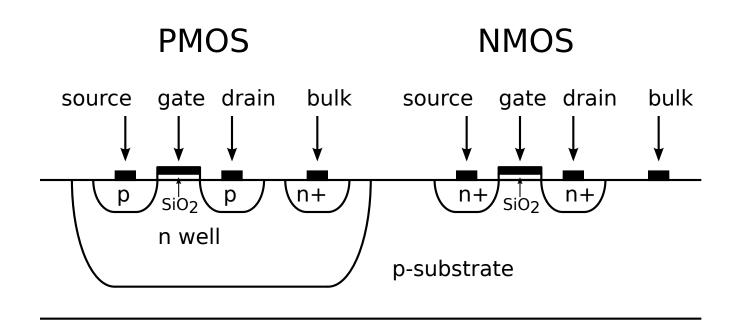

# PMOS source gate drain bulk source gate drain bulk p siO2 p n+ n+ siO2 n+ n well p-substrate

#### Drain-source voltage dependency

Channel length modulation (CLM)

Drain current increases with drain-source voltage Breakdown

## MOS operation

$$V_{GS}=0,\,V_{DS}>0\,$$

No current flow

$$V_{GS} > 0, V_{DS} >> 0$$

Surface potential at oxide-Si interface rises Source injects electrons in p region Weak inversion capacitive coupling

gate

Si-SiO<sub>2</sub>

Drain current increases exponentially with the gate-source voltage

$$V_{GS} > V_{th}, V_{DS} > V_{GS} - V_{th}$$

An n-channel is established between source and drain Drain current increases quadratically with the gate-source voltage

Short channel effects

#### Drain-source voltage dependency

Channel length modulation (CLM)

Drain current increases with drain-source voltage Breakdown

## MOS operation

$$V_{GS}=0,\,V_{DS}>0\,$$

No current flow

$$V_{GS} > 0, V_{DS} >> 0$$

Surface potential at oxide-Si interface rises Source injects electrons in p region Weak inversion capacitive coupling

gate

Si-SiO<sub>2</sub>

Drain current increases exponentially with the gate-source voltage

$$V_{GS} > V_{th}, V_{DS} > V_{GS} - V_{th}$$

An n-channel is established between source and drain Drain current increases quadratically with the gate-source voltage

#### Short channel effects

Vertical field mobility reduction (VFMR)

#### **PMOS NMOS** source gate drain gate drain bulk n+ n+n well p-substrate

#### Drain-source voltage dependency

Channel length modulation (CLM)

Drain current increases with drain-source voltage Breakdown

## MOS operation

$$V_{GS}=0,\,V_{DS}>0\,$$

No current flow

$$V_{GS} > 0, V_{DS} >> 0$$

Surface potential at oxide-Si interface rises Source injects electrons in p region Weak inversion

capacitive coupling gate Si-SiO<sub>2</sub>

Drain current increases exponentially with the gate-source voltage

$$V_{GS} > V_{th}, V_{DS} > V_{GS} - V_{th}$$

An n-channel is established between source and drain Drain current increases quadratically with the gate-source voltage

#### Short channel effects

Vertical field mobility reduction (VFMR) Velocity saturation (VS)

#### Drain-source voltage dependency

Channel length modulation (CLM)

Drain current increases with drain-source voltage Breakdown

# MOS operation

$$V_{GS}=0,\,V_{DS}>0\,$$

No current flow

$$V_{GS} > 0, V_{DS} >> 0$$

Surface potential at oxide-Si interface rises Source injects electrons in p region Weak inversion capacitive coupling

gate

Si-SiO<sub>2</sub>

Drain current increases exponentially with the gate-source voltage

$$V_{GS} > V_{th}, V_{DS} > V_{GS} - V_{th}$$

An n-channel is established between source and drain Drain current increases quadratically with the gate-source voltage

#### Short channel effects

Vertical field mobility reduction (VFMR) Velocity saturation (VS)

Drain current increases not longer quadratically with the gate-source voltage

#### **PMOS NMOS** gate drain bulk source gate drain n+ n+n well p-substrate

#### Drain-source voltage dependency

Channel length modulation (CLM)

Drain current increases with drain-source voltage Breakdown

## MOS operation

$$V_{GS}=0,\,V_{DS}>0\,$$

No current flow

$$V_{GS} > 0, V_{DS} >> 0$$

Surface potential at oxide-Si interface rises Source injects electrons in p region Weak inversion

capacitive coupling gate Si-SiO<sub>2</sub>

Drain current increases exponentially with the gate-source voltage

$$V_{GS} > V_{th}, V_{DS} > V_{GS} - V_{th}$$

An n-channel is established between source and drain Drain current increases quadratically with the gate-source voltage

#### Short channel effects

Vertical field mobility reduction (VFMR) Velocity saturation (VS)

Drain current increases not longer quadratically with the gate-source voltage

Drain-induced barrier lowering (DIBL)

#### **PMOS NMOS** gate drain bulk source gate drain n+ n well p-substrate

#### Drain-source voltage dependency

Channel length modulation (CLM)

Drain current increases with drain-source voltage Breakdown

## MOS operation

$$V_{GS}=0,\,V_{DS}>0\,$$

No current flow

$$V_{GS} > 0, V_{DS} >> 0$$

Surface potential at oxide-Si interface rises Source injects electrons in p region Weak inversion

capacitive coupling gate Si-SiO<sub>2</sub>

Drain current increases exponentially with the gate-source voltage

$$V_{GS} > V_{th}, V_{DS} > V_{GS} - V_{th}$$

An n-channel is established between source and drain Drain current increases quadratically with the gate-source voltage

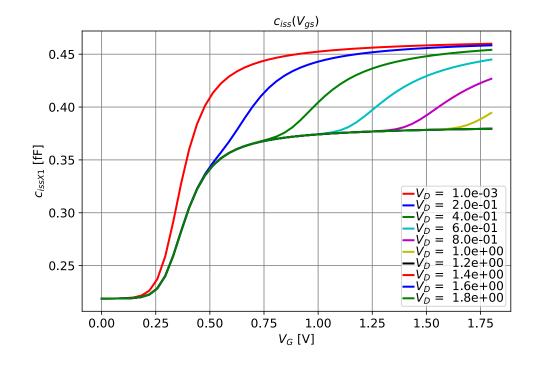

#### Short channel effects

Vertical field mobility reduction (VFMR)

Velocity saturation (VS)

Drain current increases not longer quadratically with the gate-source voltage

Drain-induced barrier lowering (DIBL)

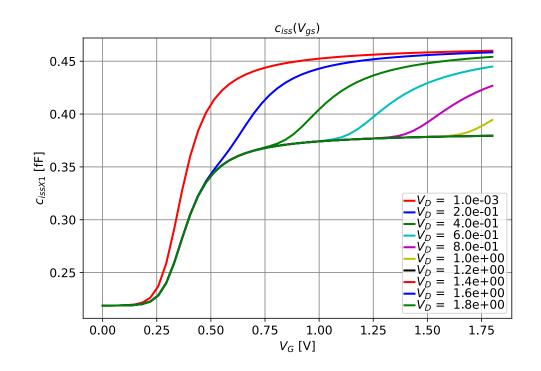

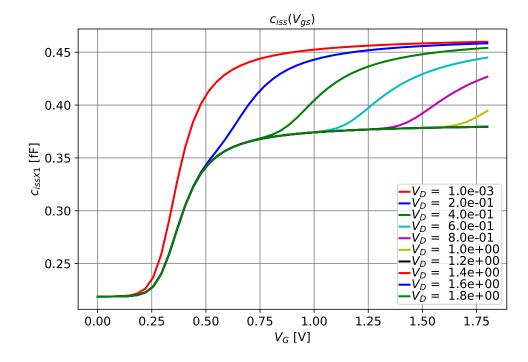

Capacitive coupling increases:

#### **PMOS NMOS** gate drain bulk source gate drain source n+ n+n well p-substrate

#### Drain-source voltage dependency

Channel length modulation (CLM)

Drain current increases with drain-source voltage Breakdown

# MOS operation

$$V_{GS}=0,\,V_{DS}>0\,$$

No current flow

$$V_{GS} > 0, V_{DS} >> 0$$

Surface potential at oxide-Si interface rises Source injects electrons in p region Weak inversion

capacitive coupling gate Si-SiO<sub>2</sub>

Drain current increases exponentially with the gate-source voltage

$$V_{GS} > V_{th}, V_{DS} > V_{GS} - V_{th}$$

An n-channel is established between source and drain Drain current increases quadratically with the gate-source voltage

#### Short channel effects

Vertical field mobility reduction (VFMR) Velocity saturation (VS)

Drain current increases not longer quadratically with the gate-source voltage

Drain-induced barrier lowering (DIBL)

Capacitive coupling increases:

Drain current increases

#### **PMOS NMOS** gate drain bulk source gate drain n+ n+n well p-substrate

#### Drain-source voltage dependency

Channel length modulation (CLM)

Drain current increases with drain-source voltage Breakdown

# MOS operation

$$V_{GS}=0,\,V_{DS}>0\,$$

No current flow

$$V_{GS} > 0, V_{DS} >> 0$$

Surface potential at oxide-Si interface rises Source injects electrons in p region Weak inversion

Drain current increases exponentially with the gate-source voltage

$$V_{GS} > V_{th}, V_{DS} > V_{GS} - V_{th}$$

An n-channel is established between source and drain Drain current increases quadratically with the gate-source voltage

#### Short channel effects

Vertical field mobility reduction (VFMR)

Velocity saturation (VS)

Drain current increases not longer quadratically with the gate-source voltage

Drain-induced barrier lowering (DIBL)

Capacitive coupling increases: Drain current increases

Design question

#### Design question

In which way do the performance parameters of a MOS transistor depend on its design parameters

#### Design question

In which way do the performance parameters of a MOS transistor depend on its design parameters

Design parameters available to the designer

## Design question

In which way do the performance parameters of a MOS transistor depend on its design parameters

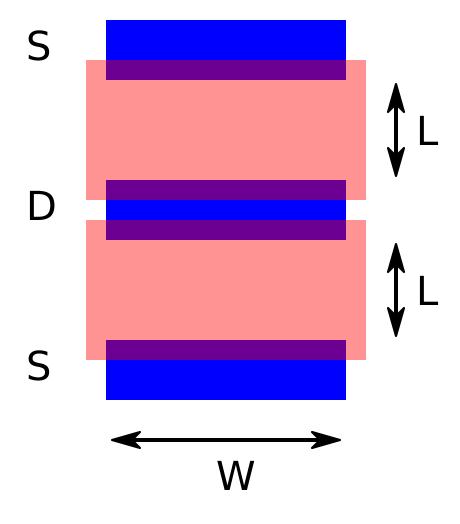

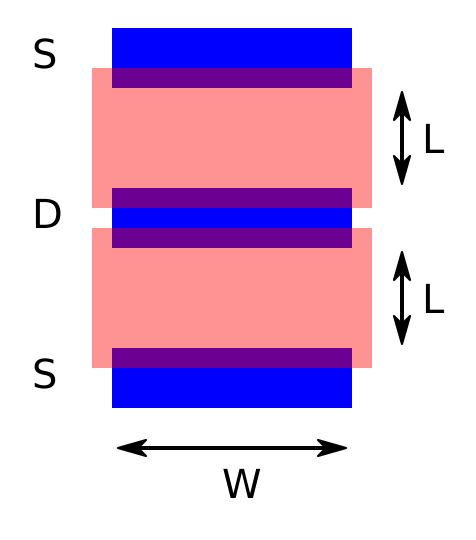

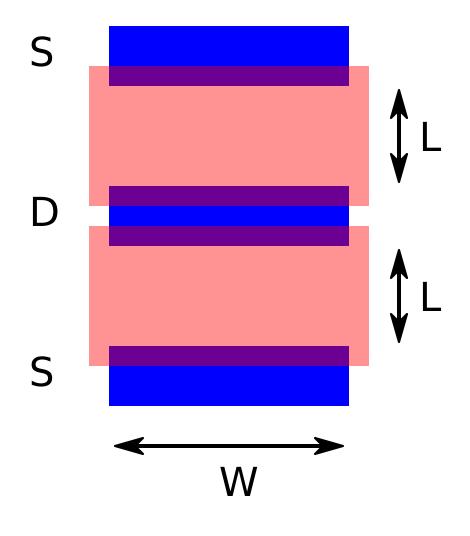

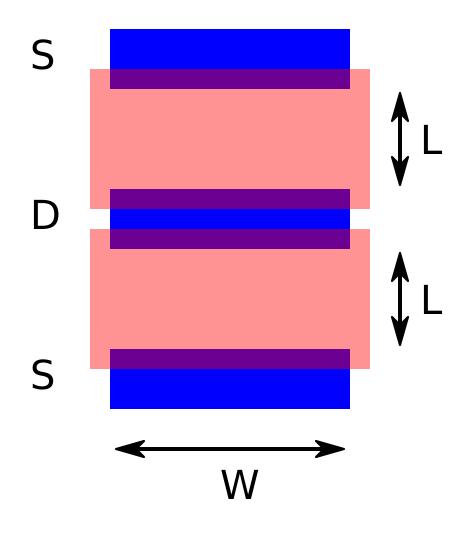

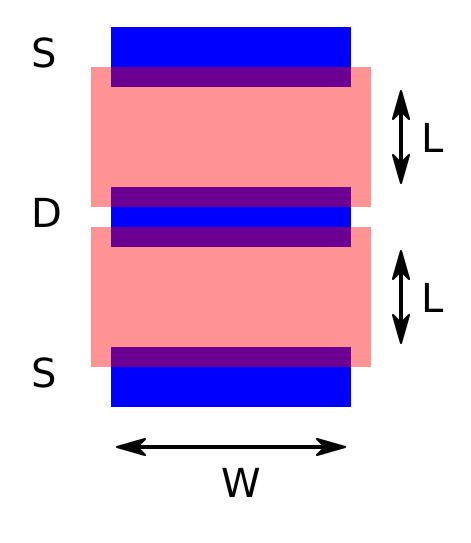

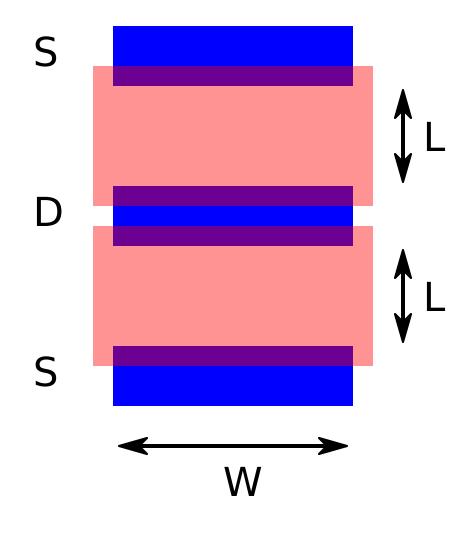

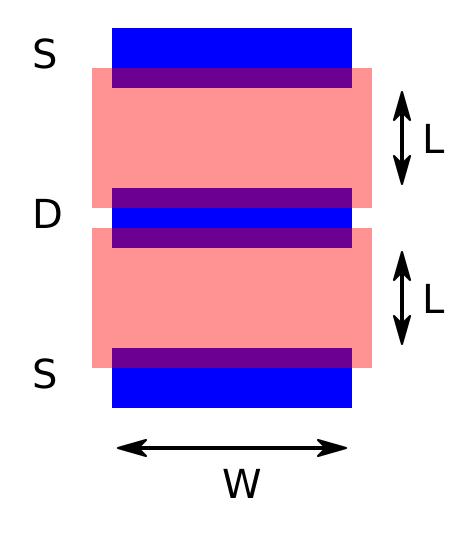

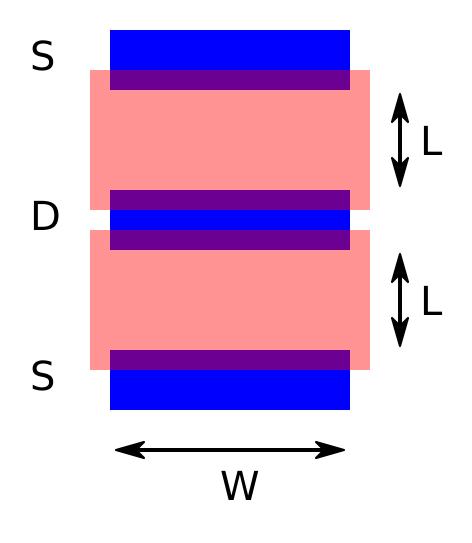

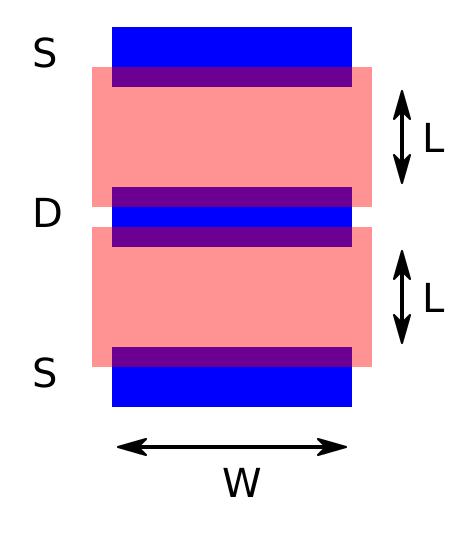

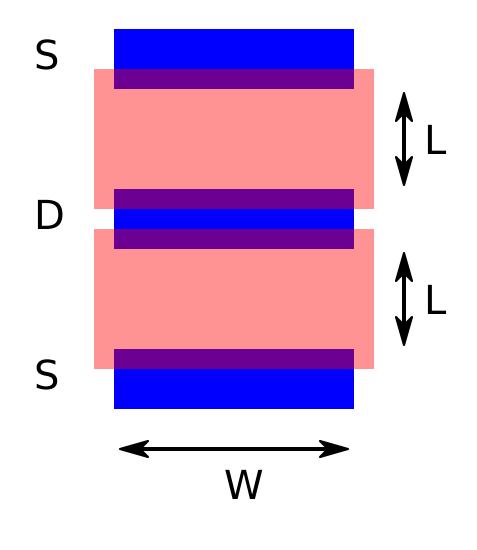

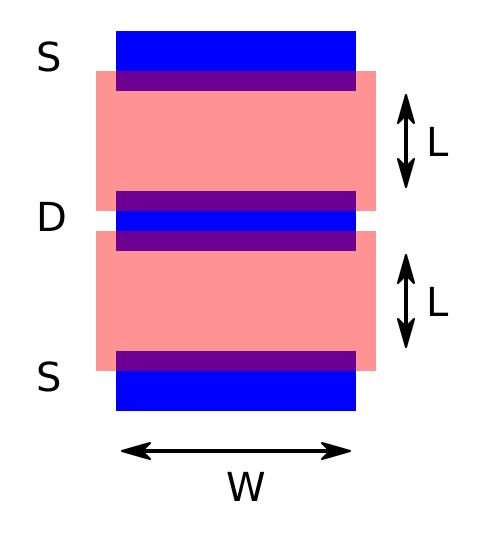

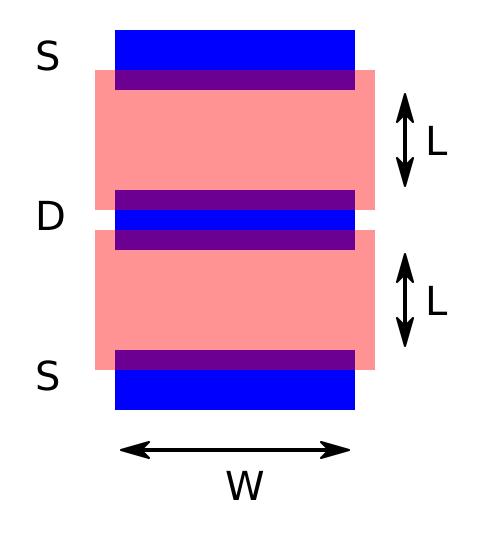

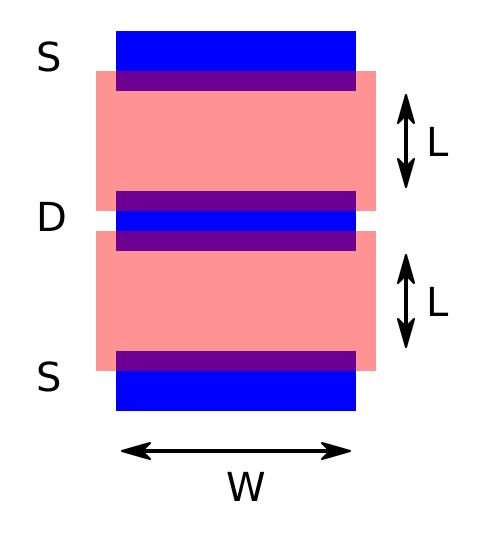

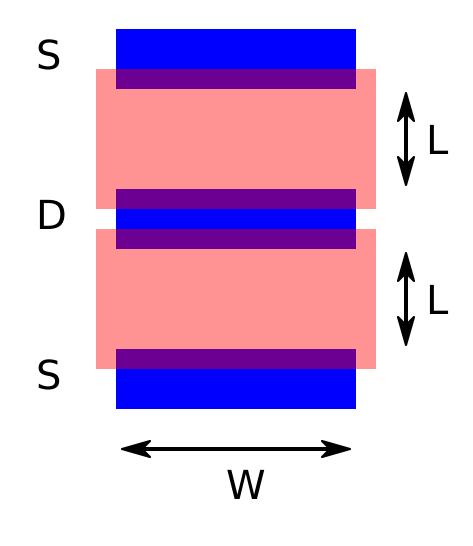

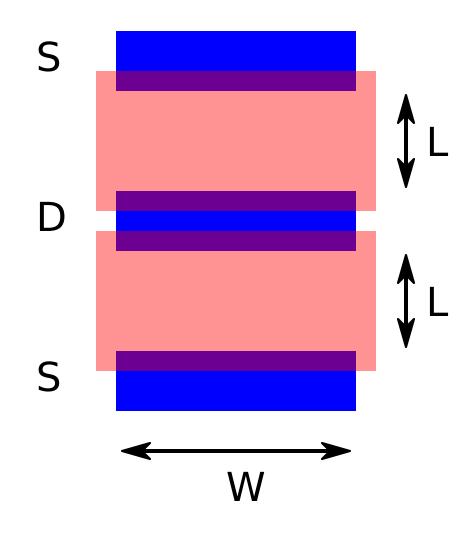

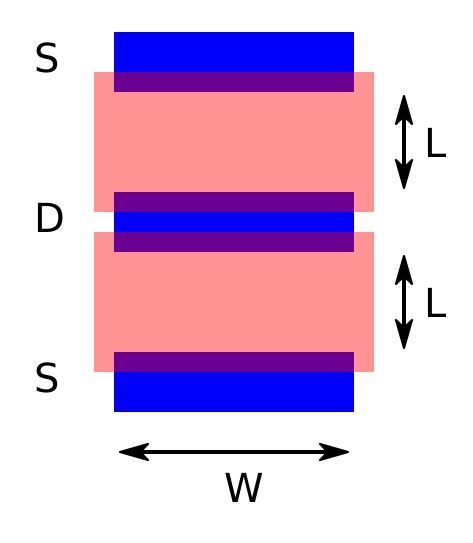

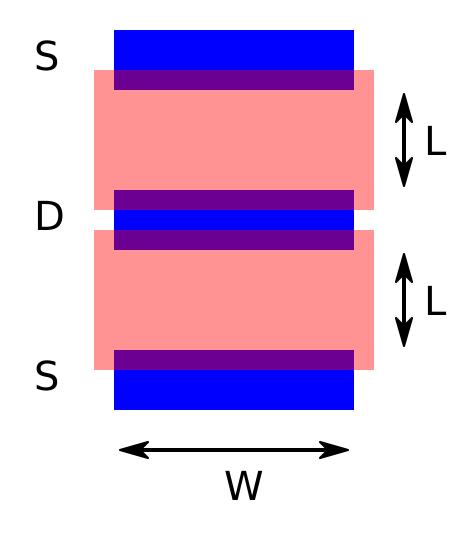

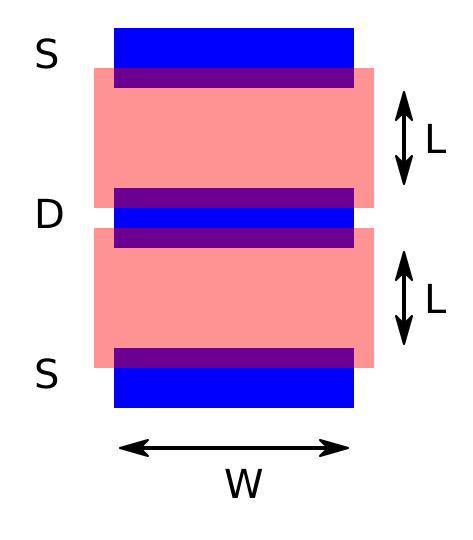

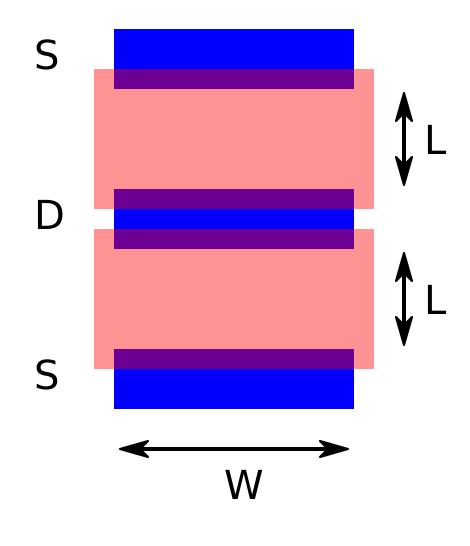

# Design parameters available to the designer

**Channel width**

## Design question

In which way do the performance parameters of a MOS transistor depend on its design parameters

## Design parameters available to the designer

Channel width **Channel length**

### Design question

In which way do the performance parameters of a MOS transistor depend on its design parameters

## Design parameters available to the designer

Channel width Channel length Number of sections

### Design question

In which way do the performance parameters of a MOS transistor depend on its design parameters

## Design parameters available to the designer

Channel width Channel length Number of sections Drain current

### Design question

In which way do the performance parameters of a MOS transistor depend on its design parameters

# Design parameters available to the designer

Channel width

Channel length

Number of sections

Drain current

Drain-source voltage

### Design question

In which way do the performance parameters of a MOS transistor depend on its design parameters

#### Methods

# Design parameters available to the designer

Channel width

Channel length

Number of sections

Drain current

Drain-source voltage

### Design question

In which way do the performance parameters of a MOS transistor depend on its design parameters

# Design parameters available to the designer

Channel width

Channel length

Number of sections

Drain current

Drain-source voltage

#### Methods

Use a design manual with graphs and tables and scale devices

#### Design question

In which way do the performance parameters of a MOS transistor depend on its design parameters

# Design parameters available to the designer

Channel width

Channel length

Number of sections

Drain current

Drain-source voltage

#### Methods

Use a design manual with graphs and tables and scale devices Useful, but generally not all situations will be covered

### Design question

In which way do the performance parameters of a MOS transistor depend on its design parameters

## Design parameters available to the designer

Channel width Channel length Number of sections Drain current Drain-source voltage

#### Methods

Use a design manual with graphs and tables and scale devices Useful, but generally not all situations will be covered

Design a device and study its performance through simulation

#### Design question

In which way do the performance parameters of a MOS transistor depend on its design parameters

# Design parameters available to the designer

Channel width

Channel length

Number of sections

Drain current

Drain-source voltage

#### Methods

Use a design manual with graphs and tables and scale devices Useful, but generally not all situations will be covered

Design a device and study its performance through simulation

Useful for finding DC operating conditions and small-signal model parameters

### Design question

In which way do the performance parameters of a MOS transistor depend on its design parameters

# Design parameters available to the designer

Channel width

Channel length

Number of sections

Drain current

Drain-source voltage

#### Methods

Use a design manual with graphs and tables and scale devices Useful, but generally not all situations will be covered

Design a device and study its performance through simulation

Useful for finding DC operating conditions and small-signal model parameters

Jupyter notebook tool

### Design question

In which way do the performance parameters of a MOS transistor depend on its design parameters

# Design parameters available to the designer

Channel width

Channel length

Number of sections

Drain current

Drain-source voltage

#### Methods

Use a design manual with graphs and tables and scale devices Useful, but generally not all situations will be covered

Design a device and study its performance through simulation

Useful for finding DC operating conditions and small-signal model parameters

Jupyter notebook tool

Use simplified design models

#### Design question

In which way do the performance parameters of a MOS transistor depend on its design parameters

## Design parameters available to the designer

Channel width Channel length Number of sections Drain current Drain-source voltage

#### Methods

Use a design manual with graphs and tables and scale devices Useful, but generally not all situations will be covered

Design a device and study its performance through simulation Useful for finding DC operating conditions and small-signal model parameters Jupyter notebook tool

Use simplified design models

Useful for design of small signal behavior: bandwidth frequency response and noise

#### Design question

In which way do the performance parameters of a MOS transistor depend on its design parameters

## Design parameters available to the designer

Channel width Channel length Number of sections Drain current Drain-source voltage

#### Methods

Use a design manual with graphs and tables and scale devices Useful, but generally not all situations will be covered

Design a device and study its performance through simulation Useful for finding DC operating conditions and small-signal model parameters Jupyter notebook tool

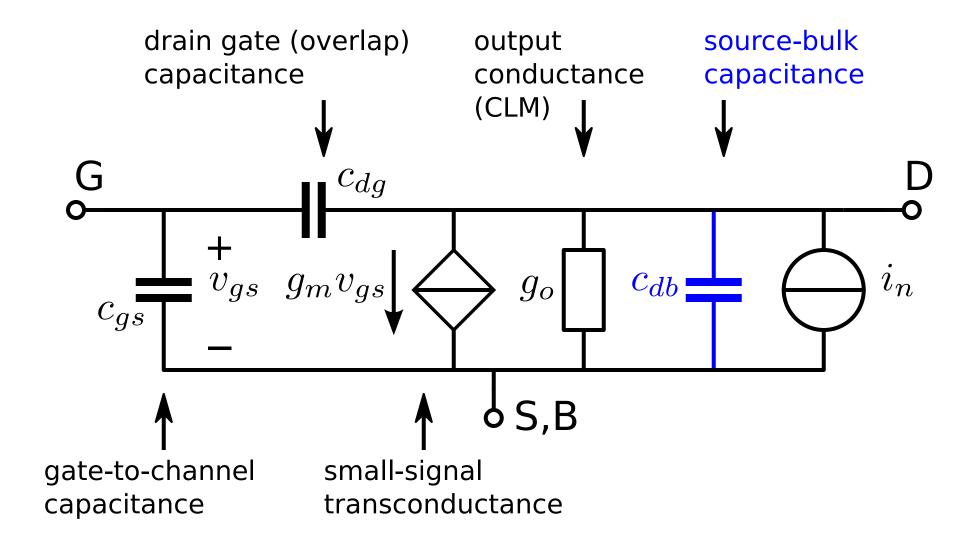

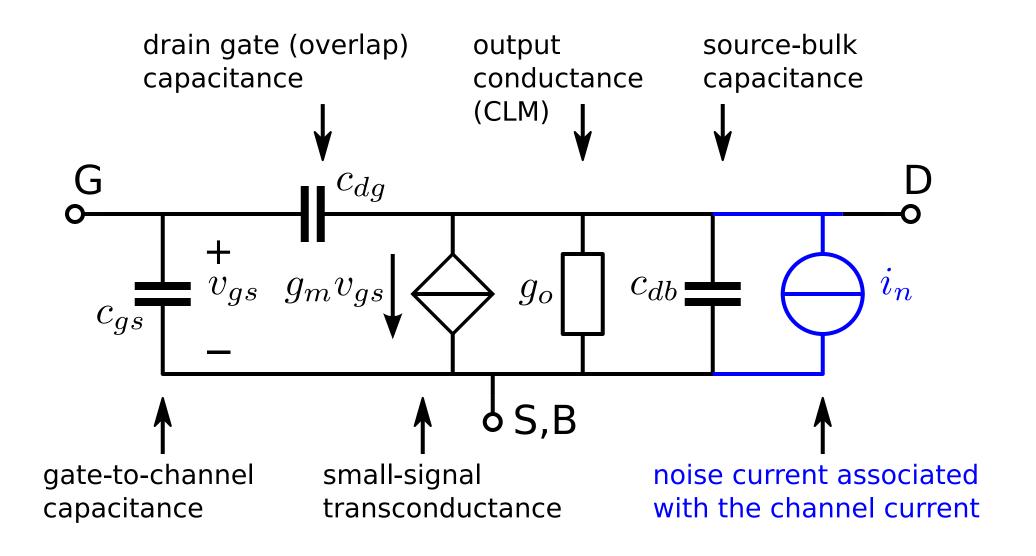

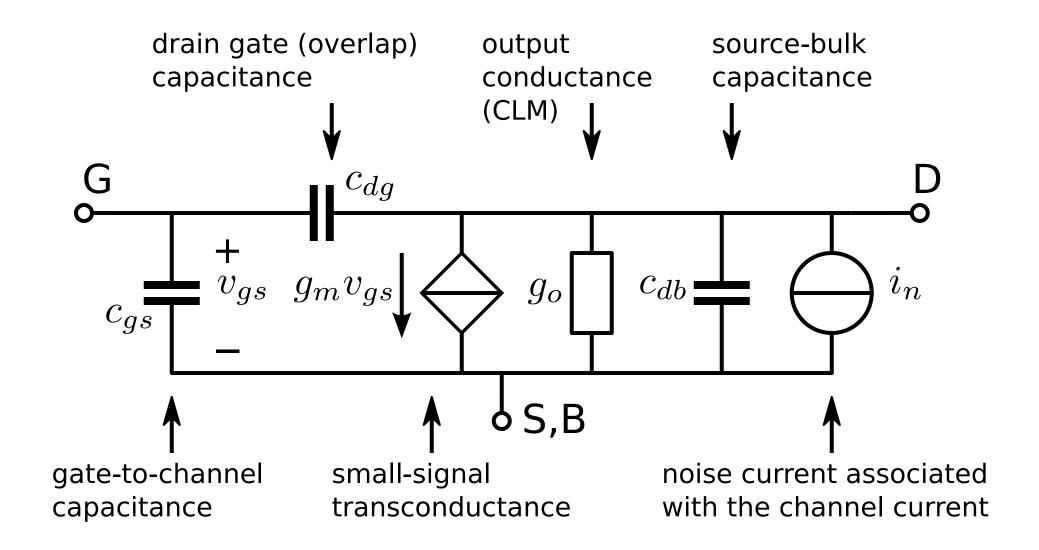

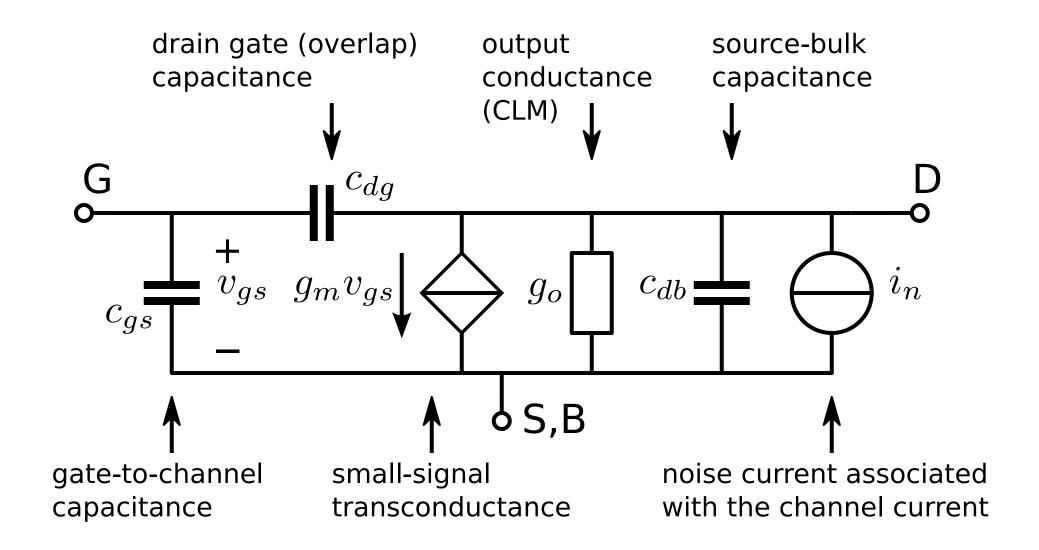

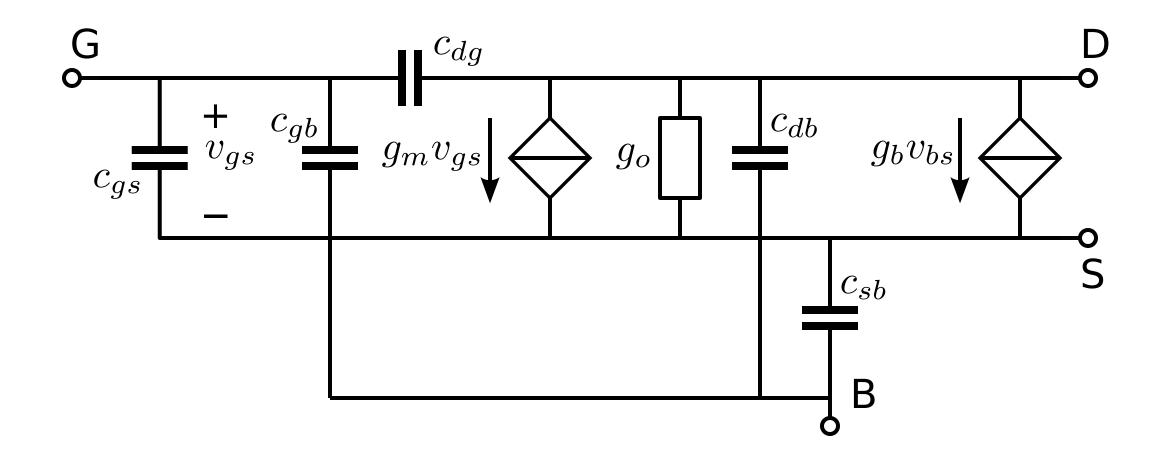

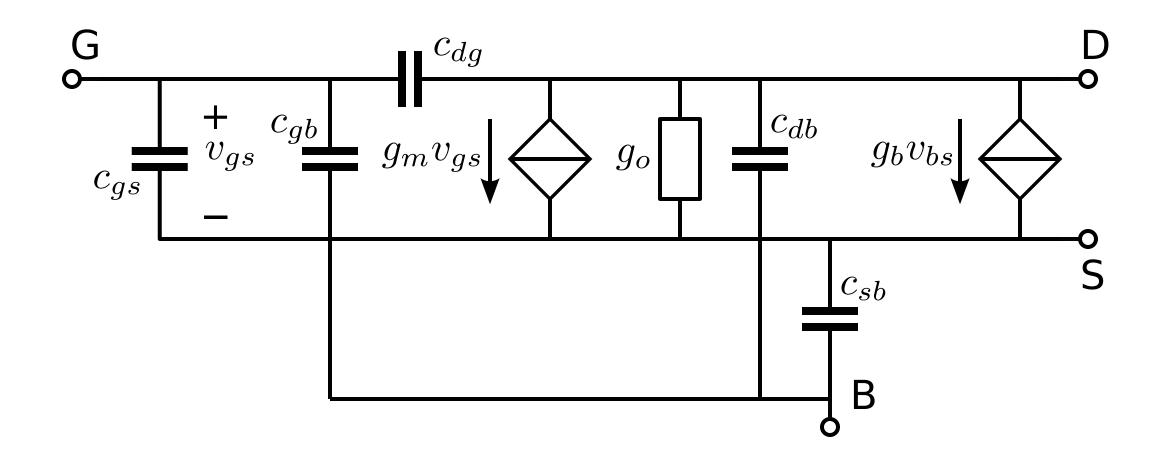

#### Use simplified design models

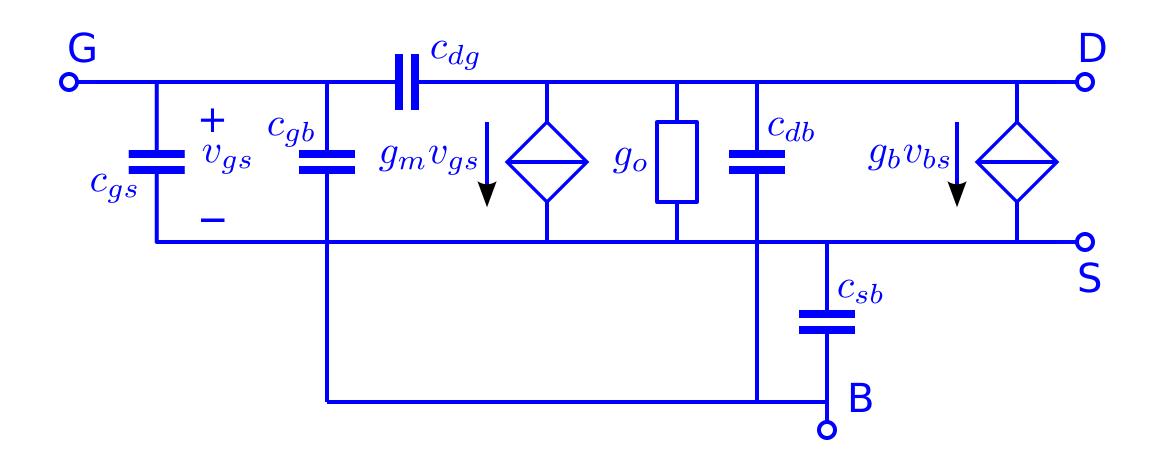

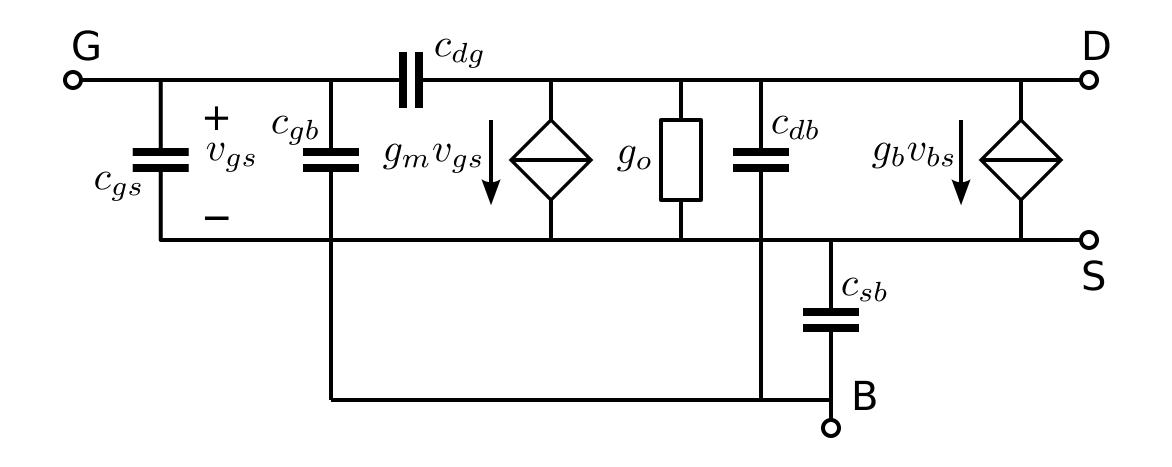

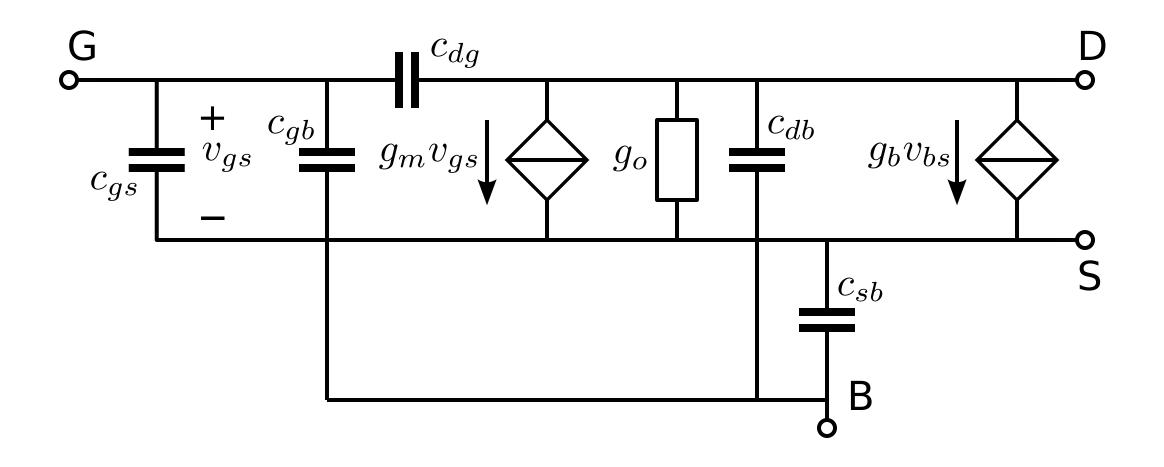

Useful for design of small signal behavior: bandwidth frequency response and noise SLiCAP small-signal models

#### Design question

In which way do the performance parameters of a MOS transistor depend on its design parameters

## Design parameters available to the designer

Channel width Channel length Number of sections Drain current Drain-source voltage

#### Methods

Use a design manual with graphs and tables and scale devices Useful, but generally not all situations will be covered

Design a device and study its performance through simulation Useful for finding DC operating conditions and small-signal model parameters Jupyter notebook tool

Use simplified design models

Useful for design of small signal behavior: bandwidth frequency response and noise SLiCAP small-signal models

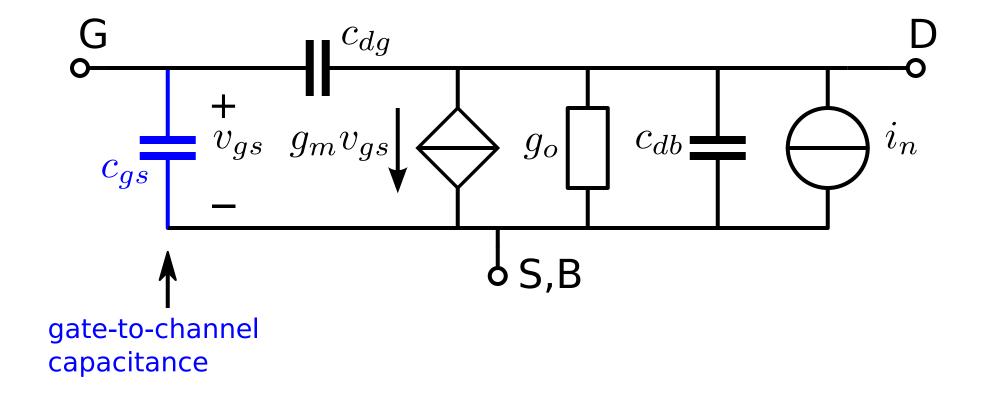

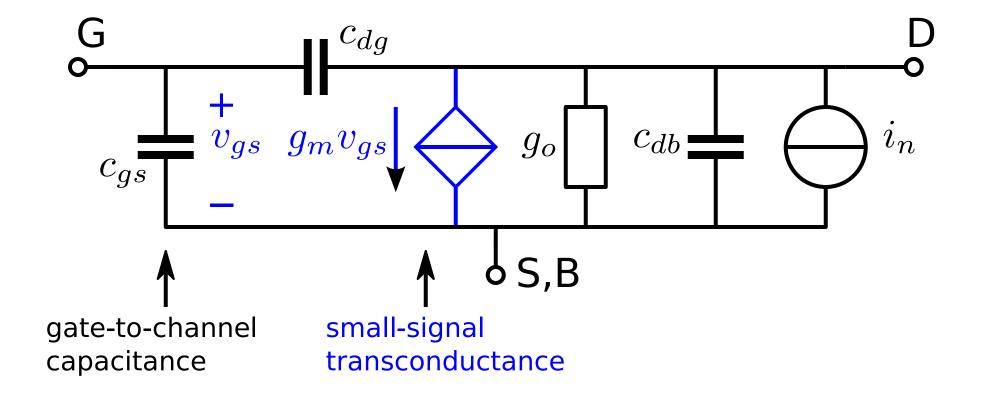

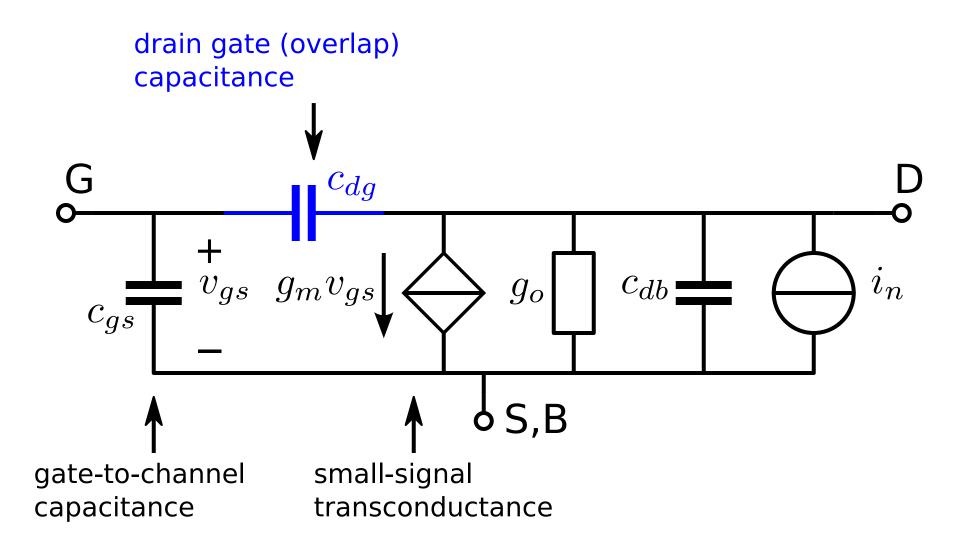

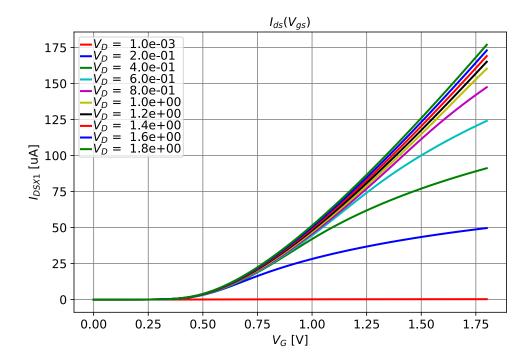

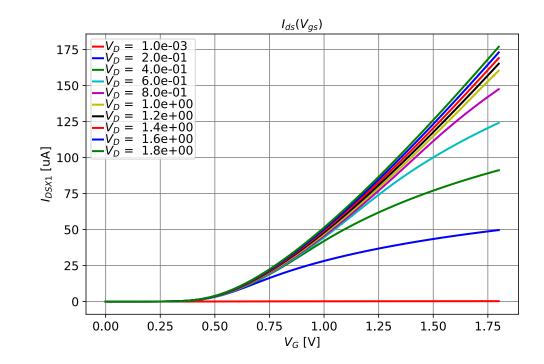

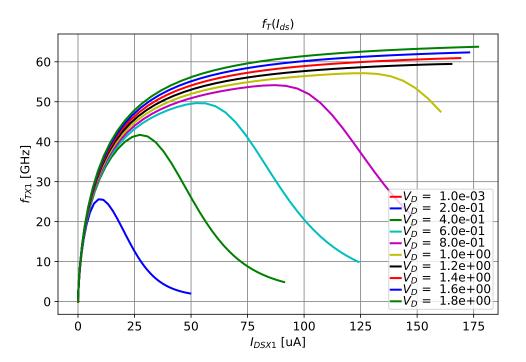

How do these model parameters depend on the device geometry and the operating conditions?

How do these model parameters depend on the device geometry and the operating conditions?

1995: C.C. Enz, F. Krummenacher and E.A. Vittoz

1995: C.C. Enz, F. Krummenacher and E.A. Vittoz

1995: C.C. Enz, F. Krummenacher and E.A. Vittoz

Models all operating regions from weak inversion to strong inversion

#### 1995: C.C. Enz, F. Krummenacher and E.A. Vittoz

Models all operating regions from weak inversion to strong inversion

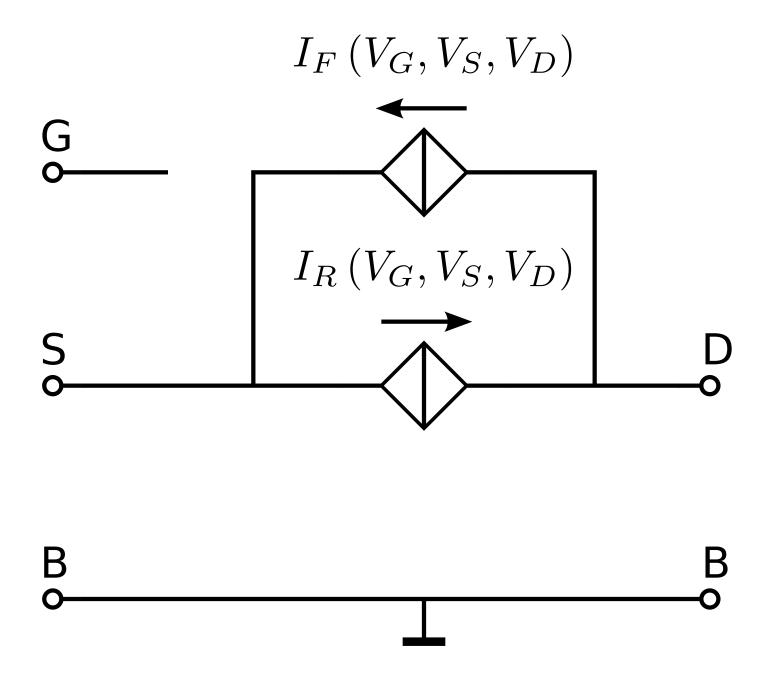

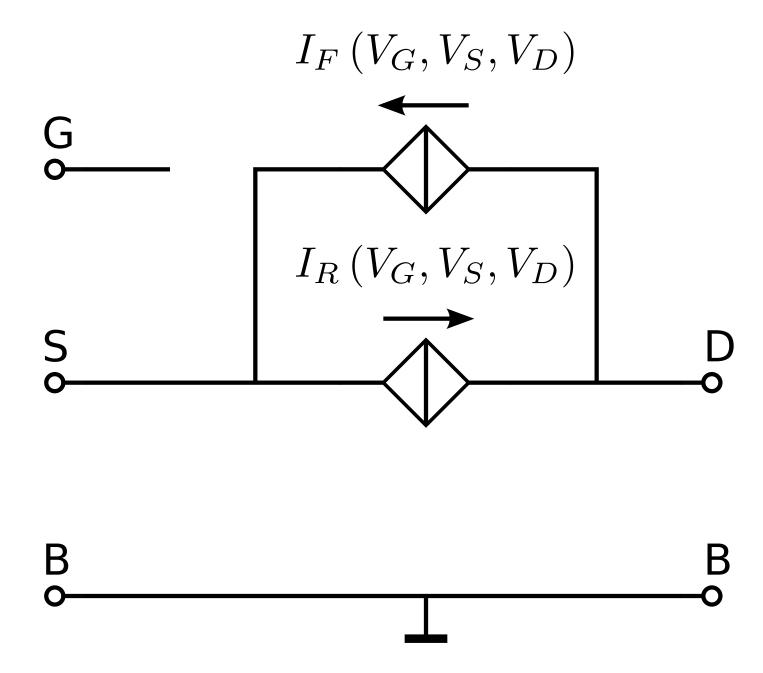

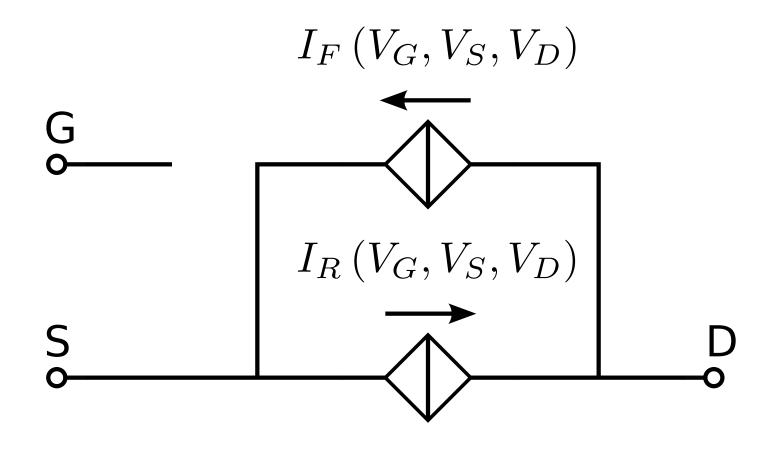

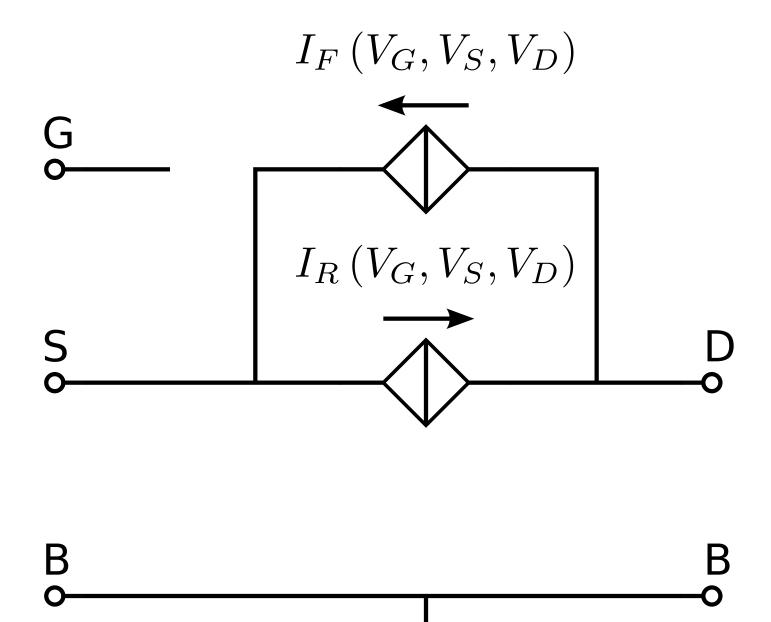

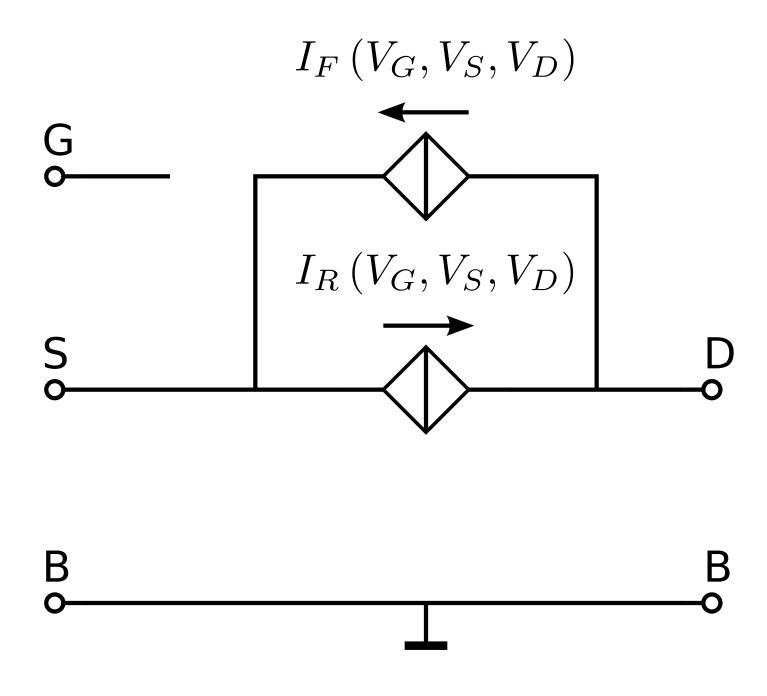

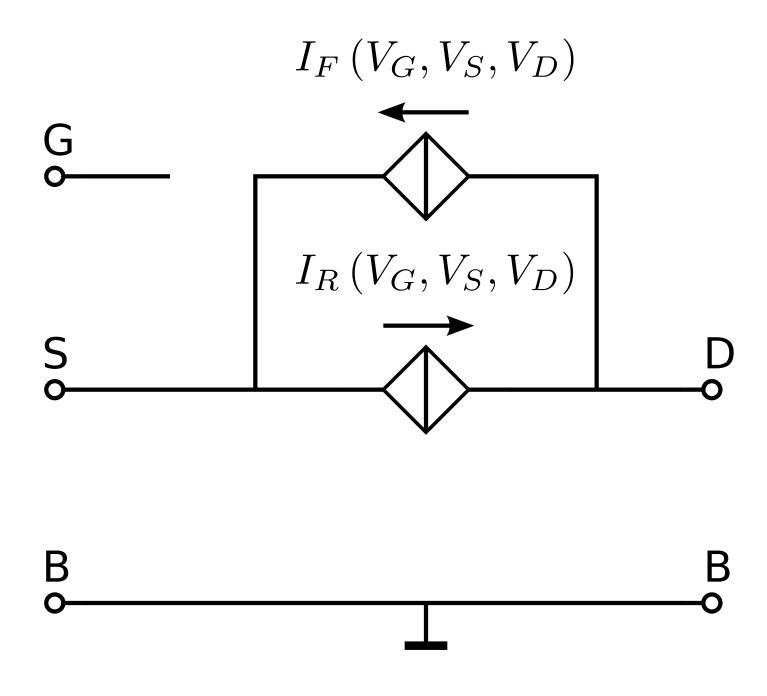

Gate, source and drain voltages with respect to the bulk

1995: C.C. Enz, F. Krummenacher and E.A. Vittoz

Models all operating regions from weak inversion to strong inversion

Gate, source and drain voltages with respect to the bulk

#### 1995: C.C. Enz, F. Krummenacher and E.A. Vittoz

Models all operating regions from weak inversion to strong inversion

Gate, source and drain voltages with respect to the bulk

Symmetrical charge-controlled model

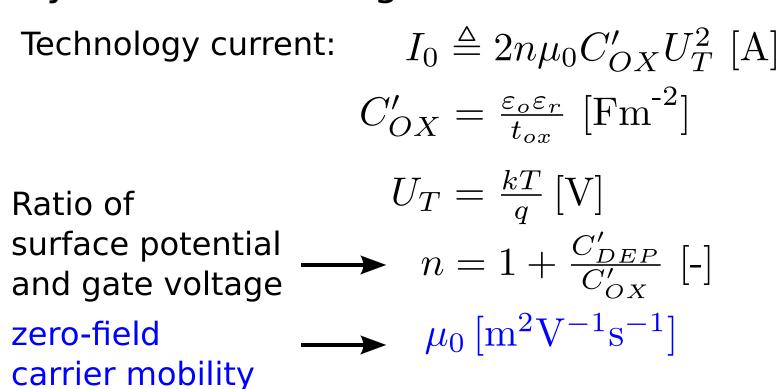

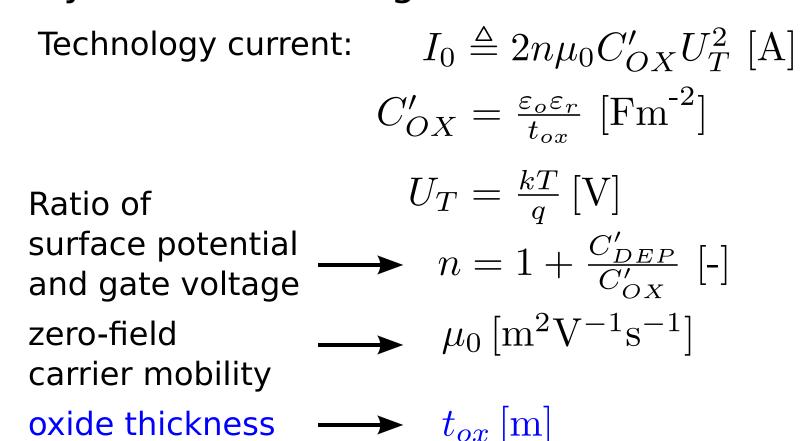

Technology current:  $I_0 \triangleq 2n\mu_0 C'_{OX} U_T^2$  [A]

#### 1995: C.C. Enz, F. Krummenacher and E.A. Vittoz

Models all operating regions from weak inversion to strong inversion

Gate, source and drain voltages with respect to the bulk

Technology current:

$$I_0 \triangleq 2n\mu_0 C'_{OX} U_T^2 \; [{\bf A}]$$

$$C'_{OX} = \frac{\varepsilon_o \varepsilon_r}{t_{ox}} [\text{Fm}^{-2}]$$

#### 1995: C.C. Enz, F. Krummenacher and E.A. Vittoz

Models all operating regions from weak inversion to strong inversion

Gate, source and drain voltages with respect to the bulk

Technology current:

$$I_0 \triangleq 2n\mu_0 C'_{OX} U_T^2 \; [{

m A}]$$

$C'_{OX} = \frac{\varepsilon_o \varepsilon_r}{t_{ox}} \; [{

m Fm}^{-2}]$   $U_T = \frac{kT}{g} \, [{

m V}]$

#### 1995: C.C. Enz, F. Krummenacher and E.A. Vittoz

Models all operating regions from weak inversion to strong inversion

Gate, source and drain voltages with respect to the bulk

Technology current:

$$I_0 \triangleq 2n\mu_0 C'_{OX} U_T^2 \ [A]$$

$C'_{OX} = \frac{\varepsilon_o \varepsilon_r}{t_{ox}} \ [Fm^{-2}]$  Ratio of  $U_T = \frac{kT}{q} \ [V]$  surface potential and gate voltage  $\longrightarrow n = 1 + \frac{C'_{DEP}}{C'_{OX}} \ [-]$

#### 1995: C.C. Enz, F. Krummenacher and E.A. Vittoz

Models all operating regions from weak inversion to strong inversion

Gate, source and drain voltages with respect to the bulk

#### 1995: C.C. Enz, F. Krummenacher and E.A. Vittoz

Models all operating regions from weak inversion to strong inversion

Gate, source and drain voltages with respect to the bulk

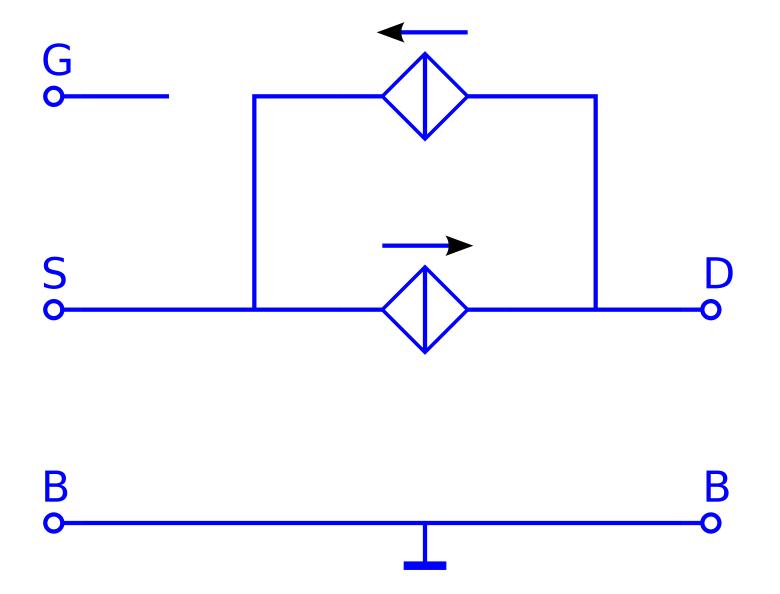

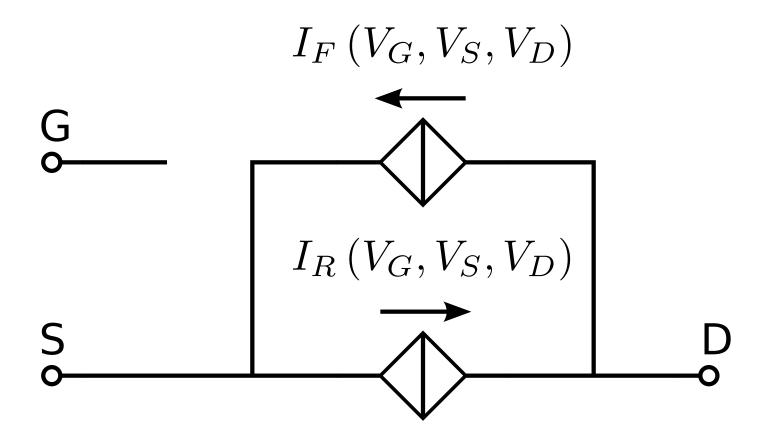

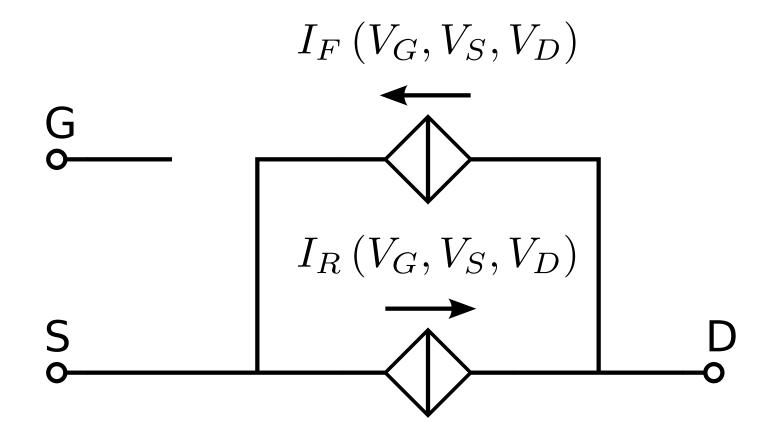

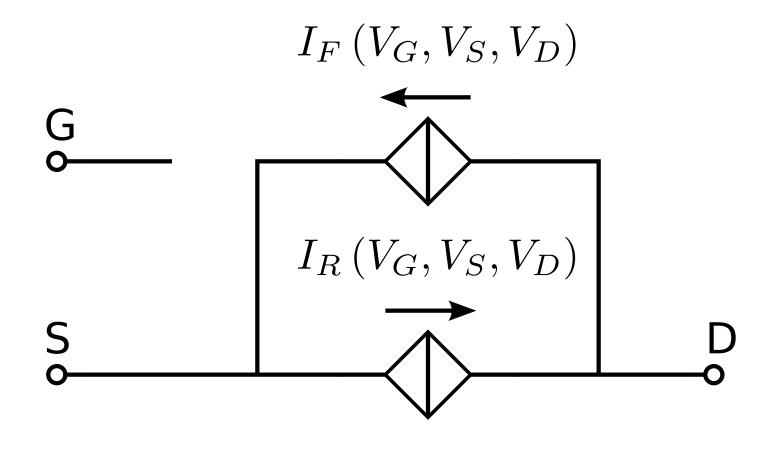

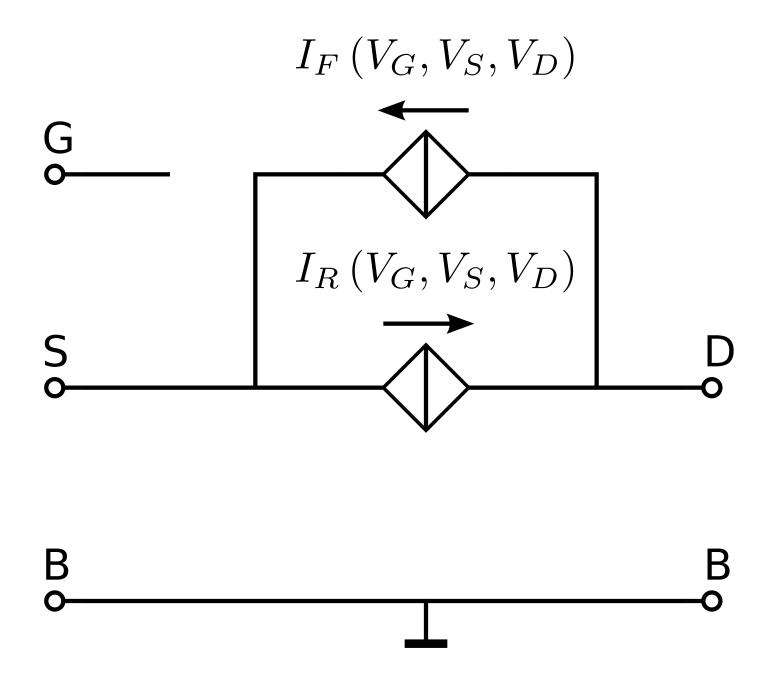

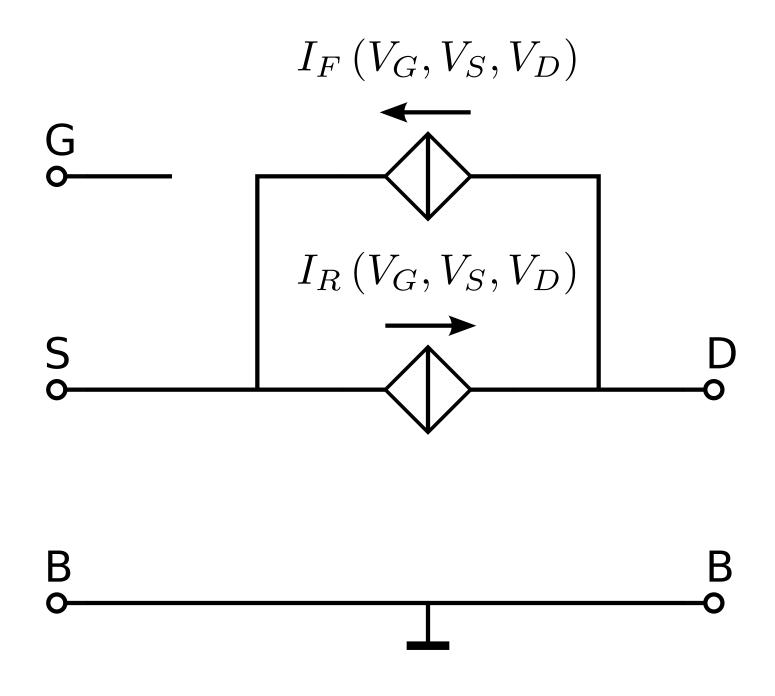

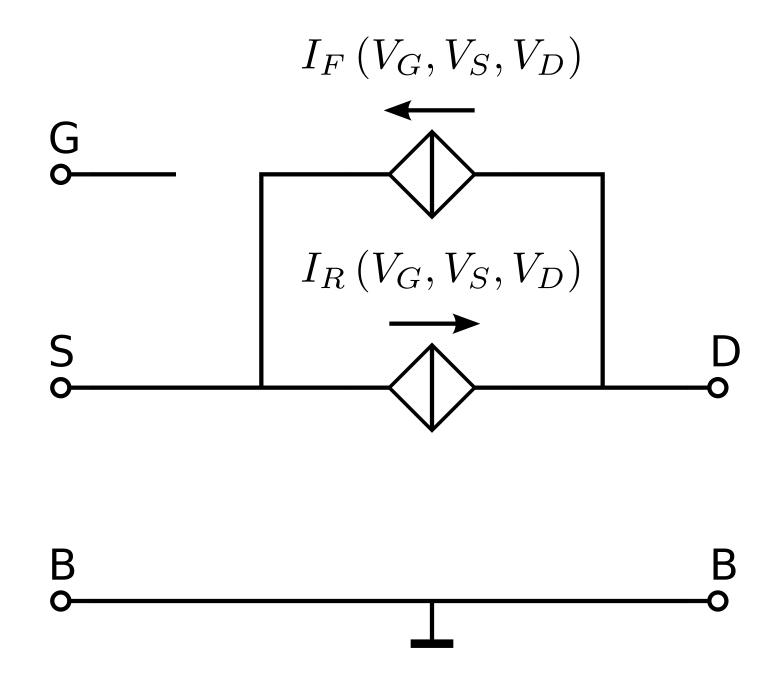

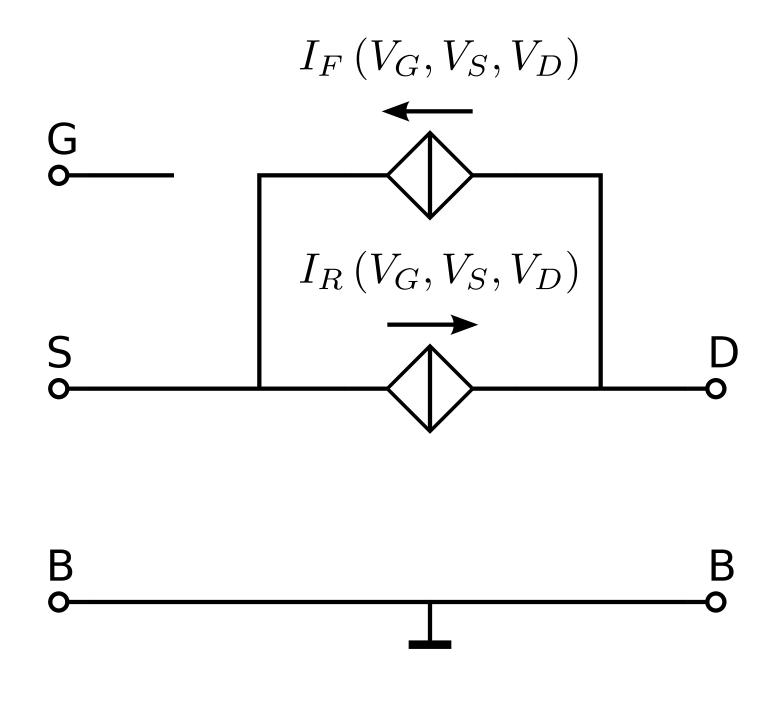

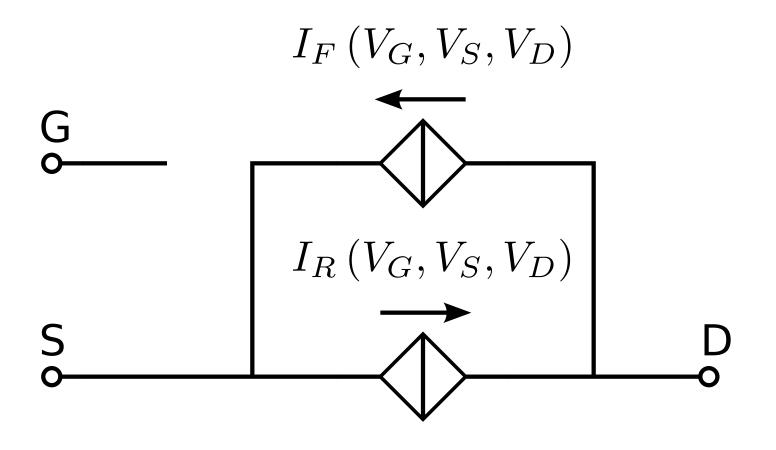

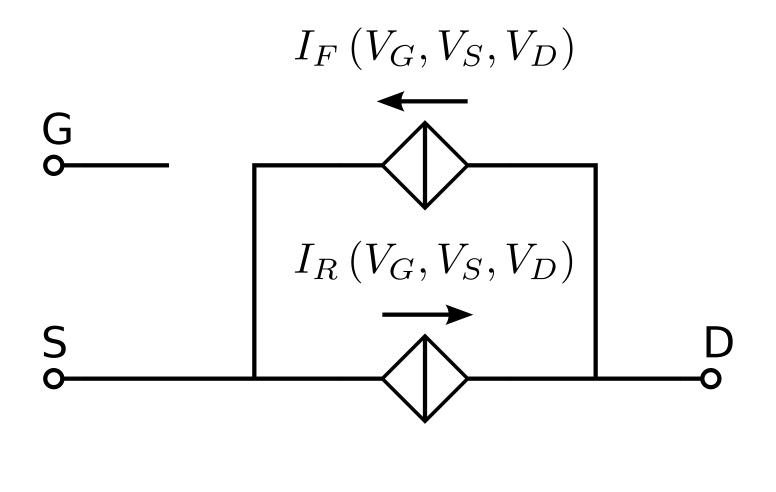

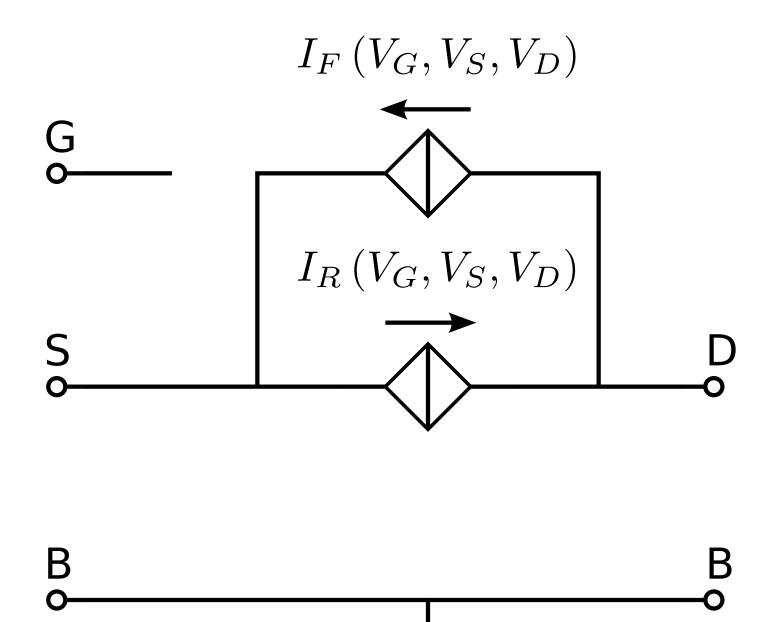

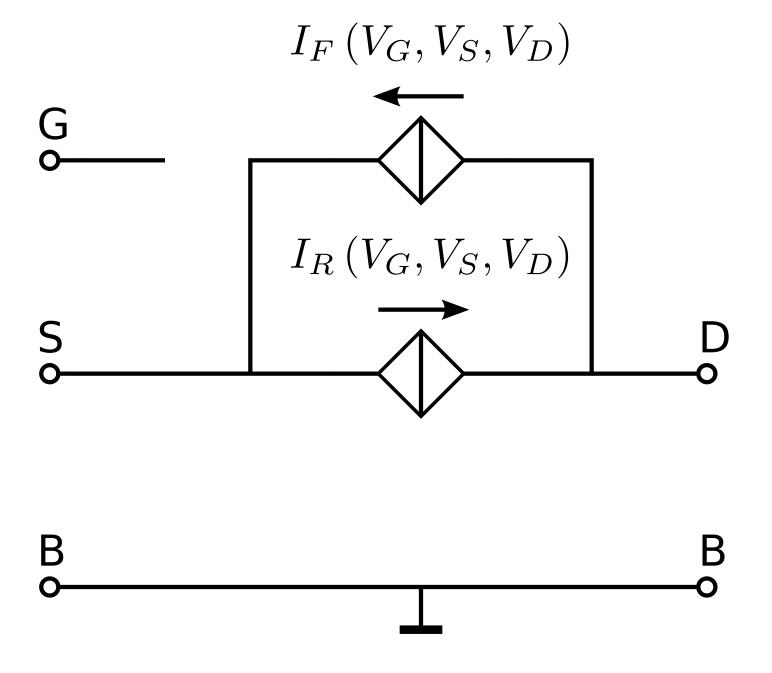

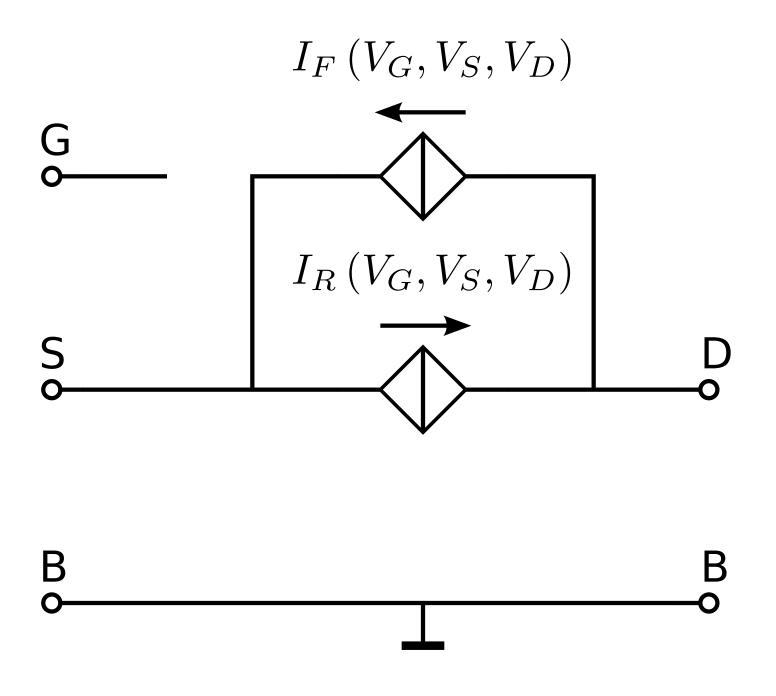

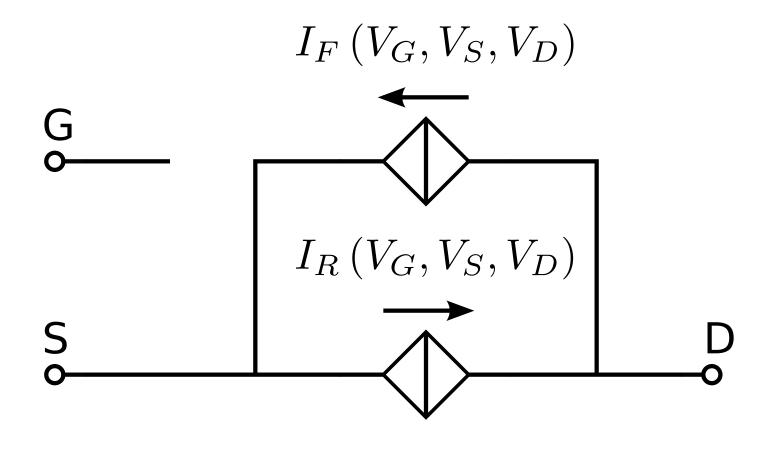

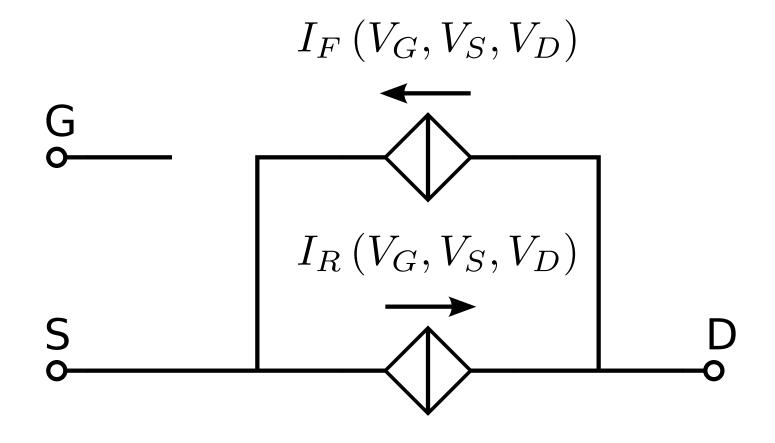

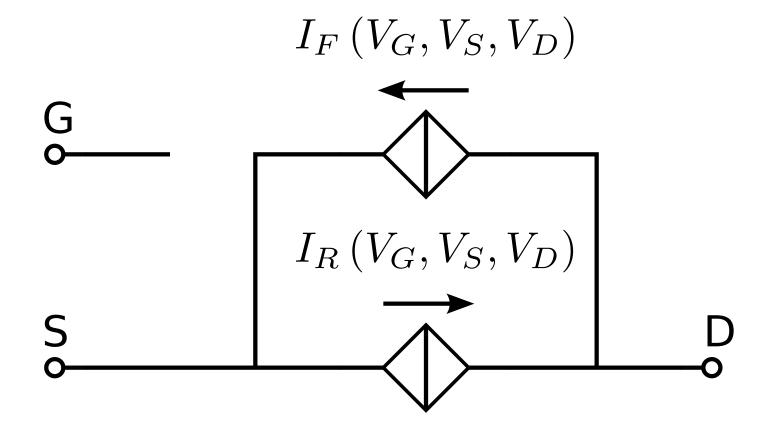

Symmetrical charge-controlled model

#### 1995: C.C. Enz, F. Krummenacher and E.A. Vittoz

Models all operating regions from weak inversion to strong inversion

Gate, source and drain voltages with respect to the bulk

Symmetrical charge-controlled model

1995: C.C. Enz, F. Krummenacher and E.A. Vittoz

## 1995: C.C. Enz, F. Krummenacher and E.A. Vittoz

$$F(x) = \left(\ln\left(1 + \exp\left(\frac{x}{2}\right)\right)\right)^2 [-]$$

1995: C.C. Enz, F. Krummenacher and E.A. Vittoz

$$F\left(x\right) = \left(\ln\left(1 + \exp\left(\frac{x}{2}\right)\right)\right)^2 \ [\text{-}]$$

this yields:  $\exp(x)$  if  $x \ll 0$ ,  $\left(\frac{x}{2}\right)^2$  if  $x \gg 0$ .

#### 1995: C.C. Enz, F. Krummenacher and E.A. Vittoz

$$F(x) = \left(\ln\left(1 + \exp\left(\frac{x}{2}\right)\right)\right)^2 [-]$$

this yields:

$$\exp(x)$$

if  $x \ll 0$ ,  $\left(\frac{x}{2}\right)^2$  if  $x \gg 0$ .

Forward and reverse inversion coefficient:

$$IC_{F,R} = F\left(\frac{V_G - V_{T0} - nV_{S,D}}{nU_T}\right)$$

[-]

#### 1995: C.C. Enz, F. Krummenacher and E.A. Vittoz

$$F(x) = \left(\ln\left(1 + \exp\left(\frac{x}{2}\right)\right)\right)^2 \quad [-]$$

this yields:

$$\exp(x)$$

if  $x \ll 0$ ,  $\left(\frac{x}{2}\right)^2$  if  $x \gg 0$ .

Forward and reverse inversion coefficient:

$$IC_{F,R} = F\left(\frac{V_G - V_{T0} - nV_{S,D}}{nU_T}\right)$$

[-]

Forward and reverse current:

$$I_{F,R} = 2n\beta_{sq}U_T^2 \frac{W}{L}IC_{F,R} \text{ [A]}$$

#### 1995: C.C. Enz, F. Krummenacher and E.A. Vittoz

$$F(x) = \left(\ln\left(1 + \exp\left(\frac{x}{2}\right)\right)\right)^2 [-]$$

this yields:

$$\exp(x)$$

if  $x \ll 0$ ,  $\left(\frac{x}{2}\right)^2$  if  $x \gg 0$ .

Forward and reverse inversion coefficient:

$$IC_{F,R} = F\left(\frac{V_G - V_{T0} - nV_{S,D}}{nU_T}\right)$$

[-]

Forward and reverse current:

$$I_{F,R} = 2n\beta_{sq}U_T^2 \frac{W}{L}IC_{F,R} [A]$$

Transconductance factor:

$$\beta_{sq} = \mu_0 C'_{OX} [AV^{-2}m^{-2}]$$

#### 1995: C.C. Enz, F. Krummenacher and E.A. Vittoz

$$F(x) = \left(\ln\left(1 + \exp\left(\frac{x}{2}\right)\right)\right)^2 [-]$$

this yields:

$$\exp(x)$$

if  $x \ll 0$ ,  $\left(\frac{x}{2}\right)^2$  if  $x \gg 0$ .

Forward and reverse inversion coefficient:

$$IC_{F,R} = F\left(\frac{V_G - V_{T0} - nV_{S,D}}{nU_T}\right)$$

[-]

Forward and reverse current:

$$I_{F,R} = 2n\beta_{sq}U_T^2 \frac{W}{L}IC_{F,R} [A]$$

Transconductance factor:

$$\beta_{sq} = \mu_0 C'_{OX} [\text{AV}^{-2} \text{m}^{-2}]$$

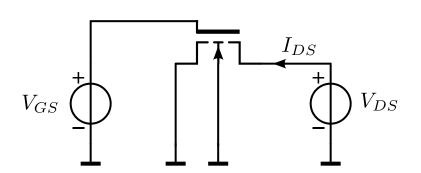

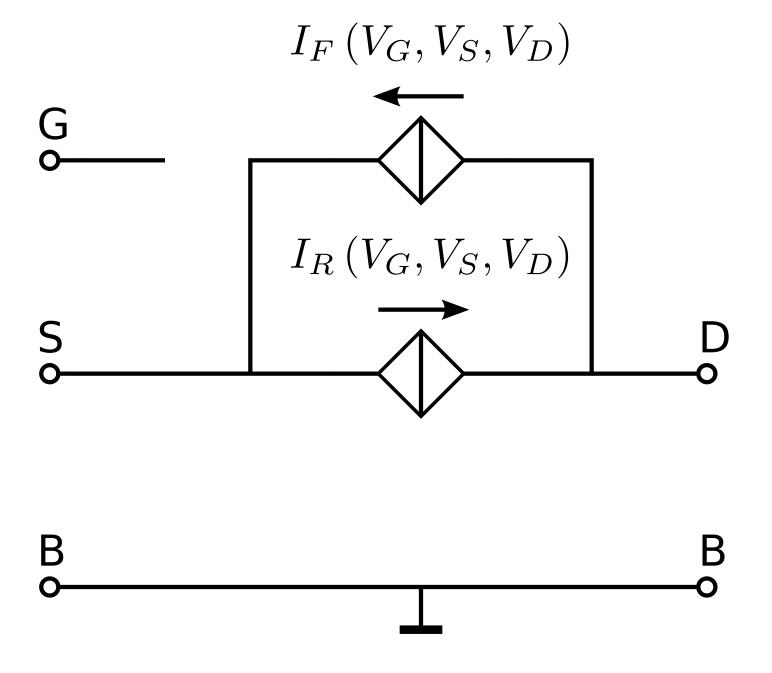

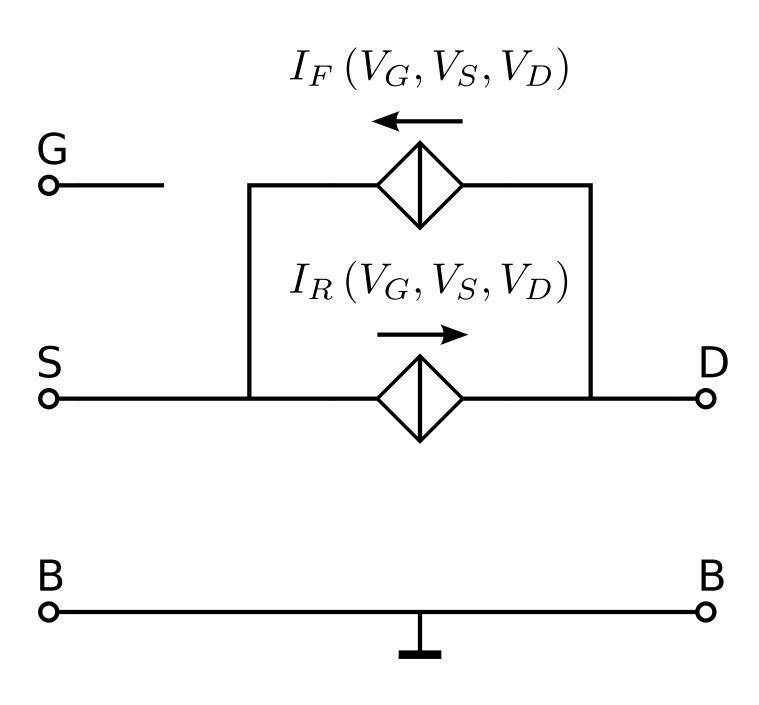

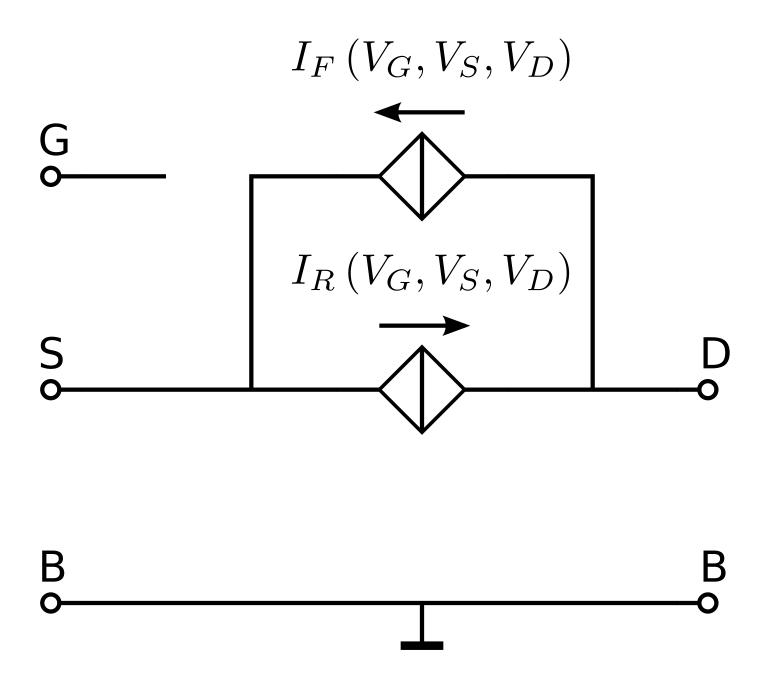

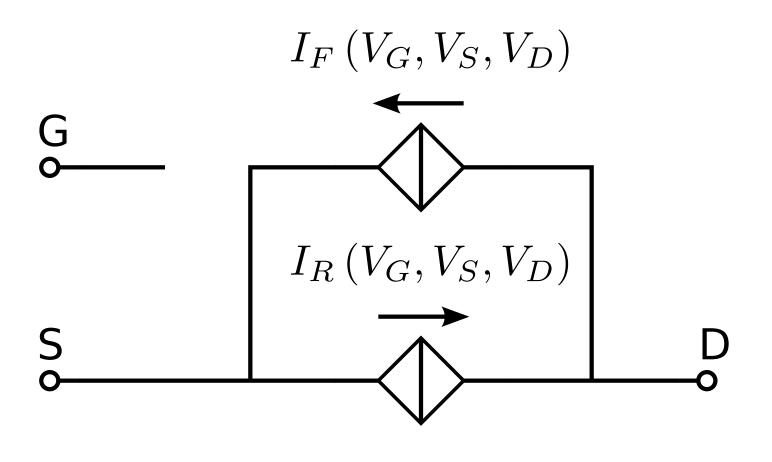

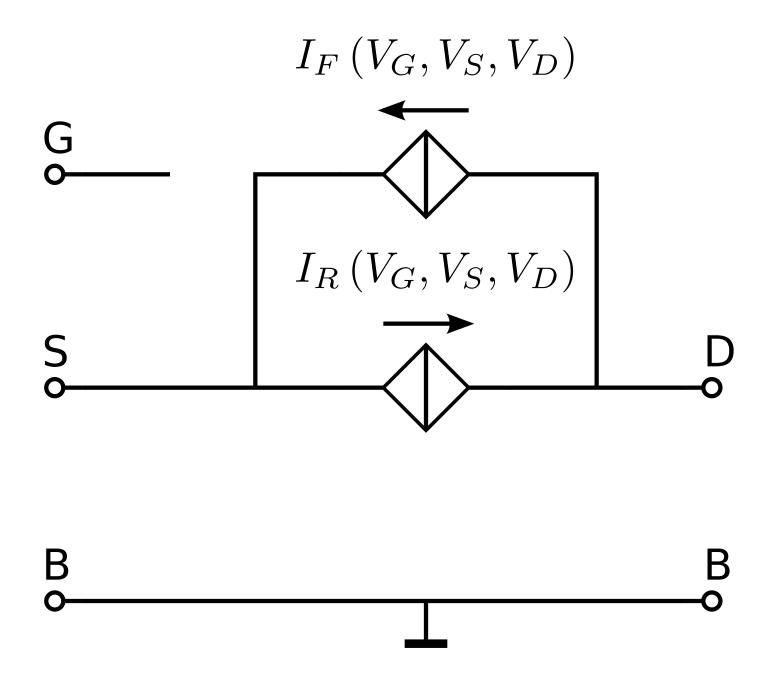

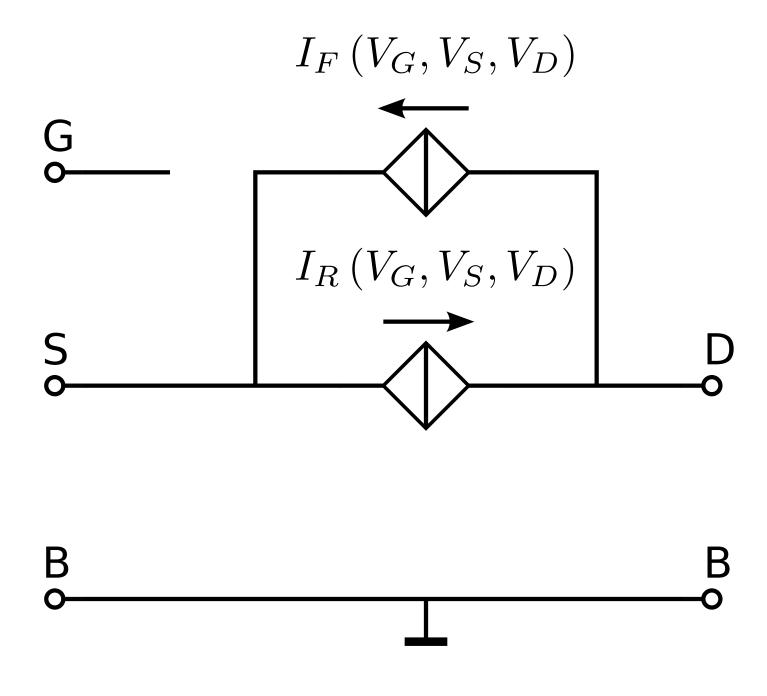

Total drain current:  $I_{DS} = I_F - I_R$  [A]

#### 1995: C.C. Enz, F. Krummenacher and E.A. Vittoz

$$F(x) = \left(\ln\left(1 + \exp\left(\frac{x}{2}\right)\right)\right)^2 [-]$$

this yields:  $\exp(x)$  if  $x \ll 0$ ,  $\left(\frac{x}{2}\right)^2$  if  $x \gg 0$ .

Forward and reverse inversion coefficient:

$$IC_{F,R} = F\left(\frac{V_G - V_{T0} - nV_{S,D}}{nU_T}\right)$$

[-]

Forward and reverse current:

$$I_{F,R} = 2n\beta_{sq}U_T^2 \frac{W}{L}IC_{F,R} [A]$$

Transconductance factor:

$$\beta_{sq} = \mu_0 C'_{OX} [\text{AV}^{-2} \text{m}^{-2}]$$

Total drain current:  $I_{DS} = I_F - I_R$  [A]

1995: C.C. Enz, F. Krummenacher and E.A. Vittoz

## 1995: C.C. Enz, F. Krummenacher and E.A. Vittoz

CLM modeled as early voltage in bipolar transistors

#### 1995: C.C. Enz, F. Krummenacher and E.A. Vittoz

CLM modeled as early voltage in bipolar transistors

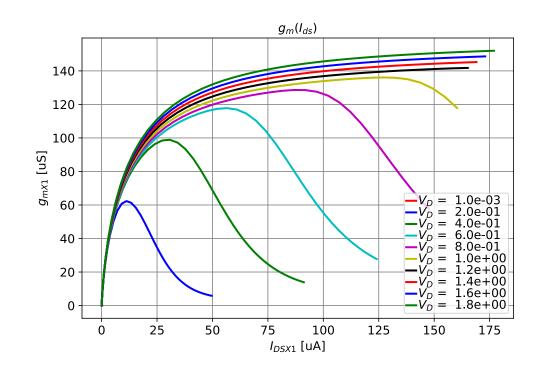

Short-channel effects (VFMR, VS) modeled as reduction of the transconductance factor

#### 1995: C.C. Enz, F. Krummenacher and E.A. Vittoz

CLM modeled as early voltage in bipolar transistors

Short-channel effects (VFMR, VS) modeled as reduction of the transconductance factor

The critical inversion coefficient is the value of the inversion coefficient at which the short-channel effects set in

#### 1995: C.C. Enz, F. Krummenacher and E.A. Vittoz

CLM modeled as early voltage in bipolar transistors

Short-channel effects (VFMR, VS) modeled as reduction of the transconductance factor

The critical inversion coefficient is the value of the inversion coefficient at which the short-channel effects set in

$$IC_{CRIT} \approx \frac{1}{\left(4nU_T\left(\theta + \frac{1}{LE_{CRIT}}\right)\right)^2} [-]$$

#### 1995: C.C. Enz, F. Krummenacher and E.A. Vittoz

CLM modeled as early voltage in bipolar transistors

Short-channel effects (VFMR, VS) modeled as reduction of the transconductance factor

The critical inversion coefficient is the value of the inversion coefficient at which the short-channel effects set in

$$IC_{CRIT} pprox rac{1}{\left(4nU_T\left( heta+rac{1}{L\ E_{CRIT}}

ight)

ight)^2} \ \ ext{[-]}$$

VFMR coefficient

#### 1995: C.C. Enz, F. Krummenacher and E.A. Vittoz

CLM modeled as early voltage in bipolar transistors

Short-channel effects (VFMR, VS) modeled as reduction of the transconductance factor

The critical inversion coefficient is the value of the inversion coefficient at which the short-channel effects set in

$$IC_{CRIT} \approx \frac{1}{\left(4nU_T\left(\theta + \frac{1}{L\ E_{CRIT}}\right)\right)^2} \ [-]$$

VFMR coefficient \int \text{critical lateral field strength}

#### 1995: C.C. Enz, F. Krummenacher and E.A. Vittoz

CLM modeled as early voltage in bipolar transistors

Short-channel effects (VFMR, VS) modeled as reduction of the transconductance factor

The critical inversion coefficient is the value of the inversion coefficient at which the short-channel effects set in

$$IC_{CRIT} \approx \frac{1}{\left(4nU_T\left(\theta + \frac{1}{L\ E_{CRIT}}\right)\right)^2}\ [-]$$

VFMR coefficient  $\int$  critical lateral field strength

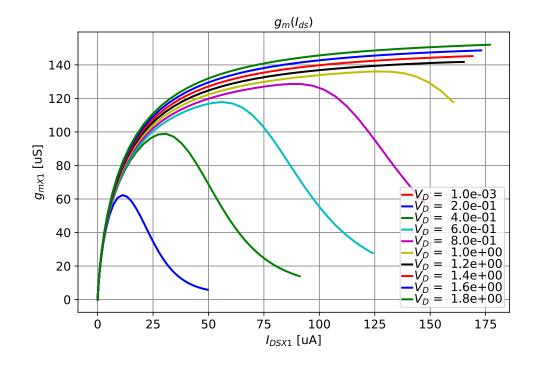

Above critical inversion the small-signal transconductance does not longer significantly increase with the drain current

#### 1995: C.C. Enz, F. Krummenacher and E.A. Vittoz

CLM modeled as early voltage in bipolar transistors

Short-channel effects (VFMR, VS) modeled as reduction of the transconductance factor

The critical inversion coefficient is the value of the inversion coefficient at which the short-channel effects set in

$$IC_{CRIT} \approx \frac{1}{\left(4nU_T\left(\theta + \frac{1}{L\ E_{CRIT}}\right)\right)^2} \ [-]$$

VFMR coefficient  $\int$  critical lateral field strength

Above critical inversion the small-signal transconductance does not longer significantly increase with the drain current

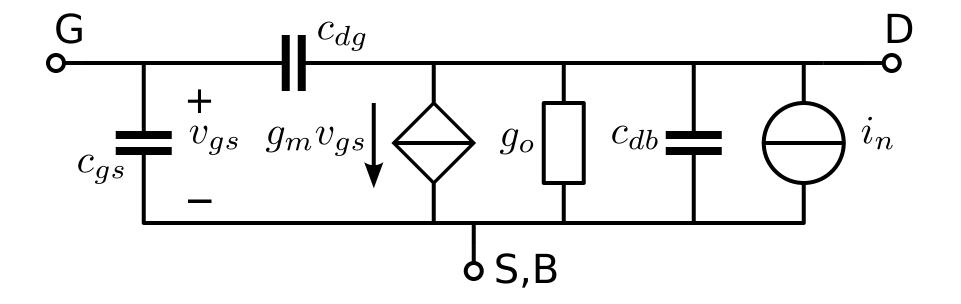

Small-signal model parameters can be expressed in terms of:

Small-signal model parameters can be expressed in terms of:

Technology parameters

Small-signal model parameters can be expressed in terms of:

Technology parameters Geometry parameters

Small-signal model parameters can be expressed in terms of:

Technology parameters Geometry parameters Operating conditions

Small-signal model parameters can be expressed in terms of:

Technology parameters

Geometry parameters

Operating conditions

Small-signal model parameters can be expressed in terms of:

Technology parameters Geometry parameters Operating conditions

Small-signal model parameters can be expressed in terms of:

Technology parameters Geometry parameters Operating conditions

Small-signal model parameters can be expressed in terms of:

Technology parameters Geometry parameters Operating conditions

Small-signal model parameters can be expressed in terms of:

Technology parameters Geometry parameters Operating conditions

Small-signal model parameters can be expressed in terms of:

Technology parameters Geometry parameters Operating conditions

Physical constants in SLiCAPmodels.lib

Physical constants in SLiCAPmodels.lib

CMOS18 technology parameters in SLiCAPmodels.lib

Physical constants in SLiCAPmodels.lib

CMOS18 technology parameters in SLiCAPmodels.lib

Device equations in subcircuit definition of the small signal model in SLiCAP.lib

Physical constants in SLiCAPmodels.lib

CMOS18 technology parameters in SLiCAPmodels.lib

Device equations in subcircuit definition of the small signal model in SLiCAP.lib